ECL-i (emitter sidestatud loogika) leiutas esmakordselt IBM 1956. aasta augustis Hannon S. Yourke poolt. Seda loogikat tuntakse ka kui praeguse režiimi loogikat, mida kasutatakse IBM 7090 ja 7094 arvutites. ECL perekond on väga kiire võrreldes digitaalne loogika peredele. Üldiselt annab see loogikaperekond levimisviivituse alla 1 ns. See on loogikaperekond, mis põhineb bipolaarsetel ristmiktransistoridel. See on kiireim loogikaperekonna ahel, mis on ligipääsetav tavapärase loogikasüsteemi kujundamiseks. Selles artiklis käsitletakse ülevaadet an emitteriga seotud loogika-ahel , rakendustega töötamine.

Mis on emitteriga seotud loogika?

Emitter-sidestatud loogika on parim BJT -põhine loogikaperekond, mida kasutatakse tavapärases loogikasüsteemi disainis. Mõnikord nimetatakse seda ka praeguse režiimi loogikaks, mis on väga kiire digitaaltehnoloogia. Üldiselt peetakse ECL-i kiireimaks loogiliseks IC-ks, kus see saavutab oma kiire töö, kasutades väga väikest pingekõikumist ja vältides ka transistoride sisenemist küllastuspiirkonda.

ECL-i rakendamine kasutab positiivset toitepinget, mida tuntakse kui PECL-i või positiivse viitega ECL-i. Varasemates ECL-väravates kasutatakse mürakindluse tõttu negatiivset pingetoiteallikat. Pärast seda sai positiivselt viidatud ECL väga kuulsaks tänu oma ühilduvamatele loogikatasemetele võrreldes TTL-loogikaperekondadega.

Emitter-sidestatud loogika hajutab tohutul hulgal staatilist võimsust, kuid selle üldine voolutarve on madal võrreldes CMOS kõrgetel sagedustel. Seega on ECL kasulik peamiselt kellajaotusahelates ja kõrgsageduspõhistes rakendustes.

Emitter Coupled Logic funktsioonid

ECL-i funktsioonid võimaldavad neid kasutada paljudes suure jõudlusega rakendustes.

- ECL pakub kahte väljundit, mis täiendavad üksteist alati, kuna ahela töö põhineb diferentsiaalvõimendil.

- See loogikaperekond sobib peamiselt monoliitsete valmistamismeetodite jaoks, kuna loogikatasemed sõltuvad takistite suhetest.

- ECL-perekonna seadmed genereerivad kavandatud funktsioonile õige ja täiendava väljundi ilma väliseid invertereid kasutamata. Järelikult vähendab see pakettide arvu ja võimsusvajadust ning vähendab ka ajalisi viivitusi.

- Diferentsiaalvõimendiga ECL-seadmed pakuvad laia jõudluse paindlikkust, nii et ECL-ahelad võimaldavad kasutada nii digitaal- kui ka lineaarahelatena.

- ECL-värava konstruktsioonil on tavaliselt kõrge ja madal sisendtakistus, mis on äärmiselt soodne nii suure ventilaatori kui ka ajamivõime saavutamiseks.

- ECL-seadmed tekitavad toiteallikas pideva voolu äravoolu, et lihtsustada toiteallika konstruktsiooni.

- ECL-i seadmed, sealhulgas avatud emitteri väljundid, võimaldavad neil lihtsalt kaasata ülekandeliini ajami võimsust.

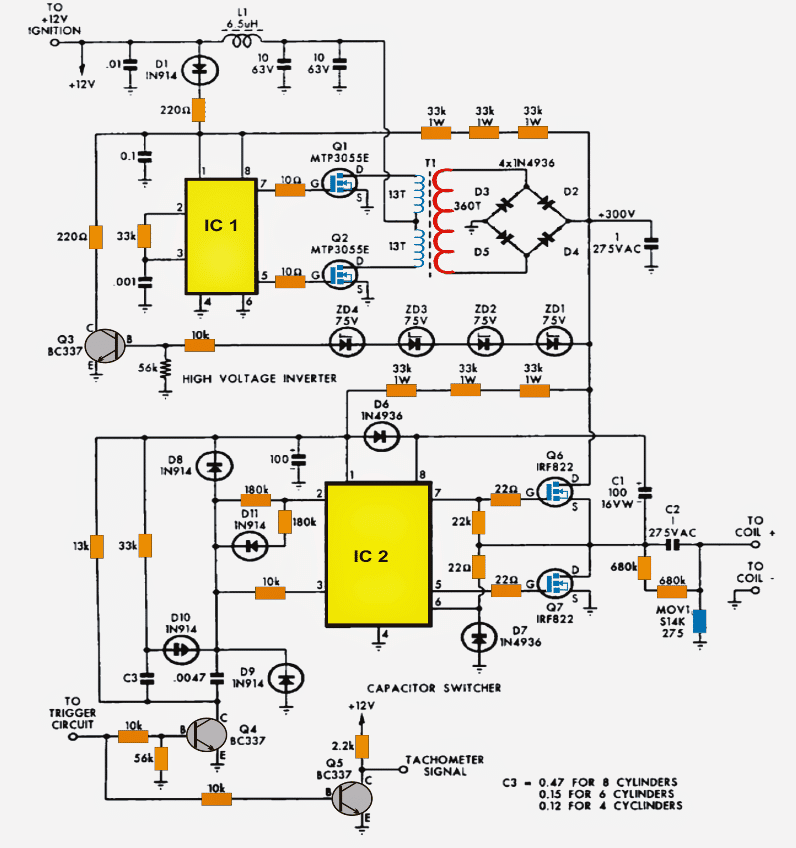

Emitter sidestatud loogikalülitus

Allpool on näidatud muunduri emitteriga ühendatud loogikalülitus, mis on konstrueeritud takistite ja transistoridega. Selles vooluringis on kahe transistori emitteri klemmid lihtsalt ühendatud voolu piirava takistusega RE, mida kasutatakse transistori küllastumise vältimiseks. Siin võetakse transistori väljund emitteri terminali asemel kollektori klemmist. Sellel vooluringil on kaks väljundit Vout (inverteeriv väljund) ja Vout2 (mitteinverteeriv väljund) ning sisendklemm nagu Vin, kus antakse kõrge või madal sisend. +Vcc = 5V.

Kuidas emitteriga seotud loogika töötab?

Emitteriga sidestatud loogika toimimine seisneb selles, et kui ECL-ahelale antakse sisend HIGH, lülitab see transistori Q1 sisse ja Q2 transistor VÄLJA, kuid Q1 transistor ei ole küllastunud. Seega tõmbab see VOUT2 väljundi asendisse HIGH ja VOUT1 väljundi väärtus on R1 languse tõttu LOW.

Samamoodi, kui ECL-ile antud VIN väärtus on MADAL, lülitab see Q1 transistori VÄLJA ja Q2 transistori SEES. Seega ei liigu Q2 transistor küllastusse. Seega muudab see VOUT1 väljundi tõmmatud väärtuseks KÕRGE ja VOUT2 väljundi väärtuse on R2 takistuse languse tõttu madal.

Vaatame, kuidas transistor Q1 ja Q2 pinge rakendamisel sisse ja välja lülituvad.

Selle ahela kaks transistorit, nagu Q1 ja Q2, on diferentsiaalvõimendina ühendatud ühise emitteri takistiga.

Selle näidisahela pingeallikad on VCC = 5,0, VBB = 4,0 & VEE = 0 V. Sisend HIGH & LOW taseme väärtused on lihtsalt määratletud kui 4,4 V ja 3,6 V. Tegelikult genereerib see vooluahel LOW väljundi & HIGH tasemed, mis on 0,6 volti kõrgemad; seda aga korrigeeritakse tegelikes ECL-ahelates.

Kui Vin on HIGH, lülitatakse Q1 transistor sisse, kuid mitte küllastunud ja Q2 transistor lülitatakse välja. Niisiis, väljundpinge nagu VOUT2 tõmmatakse 5 V-ni läbi takisti R2 ja saab näidata, et pingelang R1 takistil on umbes 0,8 V, nii et VOUT1 = 4,2 V (LOW). Lisaks VE = VOUT1 – VQ1 => 4.2V – 0.4V = 3.8V, kuna transistor Q1 on täielikult SISSE lülitatud.

Kui Vin on LOW, lülitatakse Q2 transistor sisse, kuid ei ole küllastunud ja Q1 transistor lülitatakse VÄLJA. Seetõttu tõmmatakse VOUT1 takistiga R1 5,0 V peale ja saab näidata, et VOUT2 on 4,2 V. Samuti VE => VOUT2 – VQ2 => 4,2 V – 0,8 V => 3,4 V, kuna transistor Q2 on SISSE lülitatud.

ECL-is ei ole kaks transistorit kunagi küllastunud nagu t sisend- ja väljundpinge kõikumised on üsna väikesed, näiteks 0,8 V ja sisendtakistus on kõrge ja väljundtakistus madal. See aitab ECL-il kiiremini töötada ja lühema levimisviivitusega.

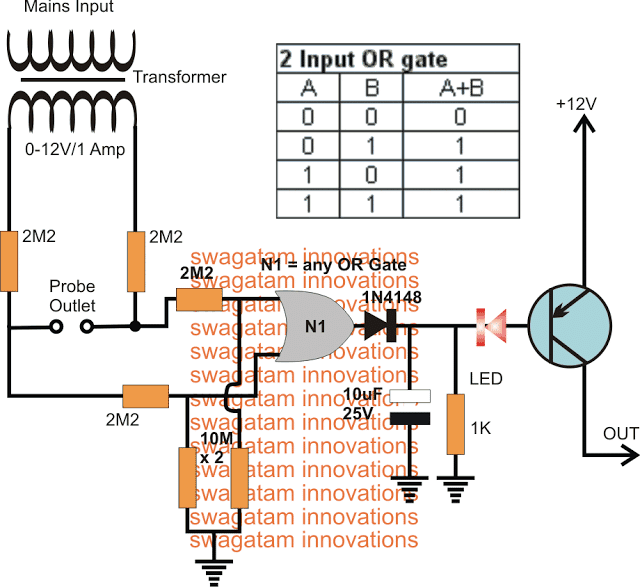

Kahe sisendiga emitteriga ühendatud loogika VÕI/NOR väravaahel

Kahe sisendiga emitteriga ühendatud loogika-VÕI/NOR-väravahel on näidatud allpool. See ahel on loodud ülaltoodud inverteri vooluringi muutmise teel. Modifikatsioon toimub lisatransistori lisamisega sisendi poolele.

Selle vooluringi töö on väga lihtne. Kui nii Q1 kui ka Q2 transistori sisendid on madalad, muudab väljund1 (Vout1) väärtuse KÕRGE. Niisiis, see Vout1 vastab NOR-värava väljundile.

Samal ajal, kui Q3 transistor on sisse lülitatud, muudab see teise väljundi (Vout2) HIGH-ks. Niisiis, see Vou2 väljund vastab VÕI värava väljundile.

Samamoodi, kui mõlemad Q1 ja Q2 transistoride sisendid on HIGH, lülitab see sisse Q1 ja Q2 transistorid ja annab madala väljundi VOUT1 terminalis.

Kui Q3 transistor on selle toimingu ajal VÄLJA lülitatud, annab see VOUT2 terminalis suure väljundi. Niisiis, VÕI/NOR-värava tõepära tabel on toodud allpool.

|

Sisendid |

Sisendid | VÕI |

NOR |

|

A |

B | Y | Y |

|

0 |

0 | 0 | 1 |

|

0 |

1 | 1 |

0 |

| 1 | 0 | 1 |

0 |

| 1 | 1 | 1 |

0 |

Emitter-sidestatud loogikakarakteristikud

ECL-i omadused hõlmavad järgmist.

- Võrreldes TTL-iga on ECL-il kiirem levimisaeg vahemikus 0,5 kuni 2 ns. Kuid emitteriga ühendatud loogiline võimsuse hajumine on suurem kui TTL-iga, näiteks 30 mW.

- ECL-i sisend-väljundpingel on väike kõikumine, näiteks 0,8.

- ECL-i sisendtakistus on kõrge ja väljundtakistus madal; järelikult muudab transistor oma olekuid väga kiiresti.

- ECL-i ventilaatori väljalaskevõime on suur ja värava viivitused väikesed.

- ECL-i o/p-loogika muutub madalast olekust KÕRGE, kuid nende olekute pingetasemed varieeruvad TTL-i ja EC-i vahel.

- ECL-i mürakindlus on 0,4 V.

Eelised ja miinused

The emitteriga seotud loogika eelised arutatakse allpool.

- ECL-i fanout on 25, mis on TTL-iga võrreldes parem ja CMOS-iga võrreldes madal.

- ECL-i keskmine levimise viivitusaeg on 1 kuni 4 ns, mis on parem võrreldes nii CMOS-i kui ka

- TTL. Seetõttu nimetatakse seda kiireimaks loogikapereks.

- Kui emitteri BJT-d on ühendatud loogika väravad töötavad aktiivses piirkonnas, siis on neil kõigi loogikaperekondadega võrreldes maksimaalne kiirus.

- ECL-väravad genereerivad täiendavaid väljundeid.

- Voolu lülitusnaelu toitejuhtmetes pole.

- Väljundeid saab juhtmega VÕI funktsiooni tagamiseks ühiselt ühendada.

- ECL parameetrid ei muutu temperatuuriga palju.

- Ei. ainsa kiibi kaudu juurdepääsetavate funktsioonide arv on kõrge.

The emitteriga seotud loogika puudused arutatakse allpool.

- Sellel on äärmiselt väiksem müravaru, st ±200 mV.

- Võrreldes teiste loogikaväravatega on võimsuse hajumine kõrge.

- Teiste loogikaperekondadega liidestamiseks on vajalikud taseme lülitid.

- Fanout piirab mahtuvuslikku laadimist.

- Võrreldes sellega TTL , ECL väravad on kallid.

- Võrreldes CMOS-i ja TTL-iga on ECL-mürakindlus halvim.

Rakendused

Emitter-sidestatud loogika rakendused hõlmavad järgmist.

- Emitter-sidestatud loogikat kasutatakse loogika- ja liidesetehnoloogiana ülikiiretes sideseadmetes, nagu fiiberoptilised transiiveri liidesed, Etherneti ja ATM-i (asünkroonne edastusrežiim) võrgud.

- ECL on BJT-l põhinev loogikaperekond, kus selle kiire töö saab saavutada suhteliselt väikese pinge kõikumise abil ja vältides transistoride liikumist küllastuspiirkonda.

- ECL-i kasutatakse ASLT-ahelate tegemisel IBM 360/91-s.

- ECL väldib virnastatud transistoride kasutamist, kasutades inverteri funktsiooni saavutamiseks primaar- ja sekundaartransistoride vahelist üheotsalist biasi ja positiivset tagasisidet.

- ECL-i kasutatakse ülikiires elektroonikas.

Seega on see ülevaade emitteriga seotud loogikast või ECL – ahel, töö, omadused, omadused ja rakendused. ECL on teiste digitaalsete loogikaperekondadega võrreldes väga kiireim BJT-l põhinev loogikaperekond. See saavutab oma maksimaalse töökiiruse, kasutades väikest pinge kõikumist ja vältides transistoride liikumist küllastuspiirkonda. See loogikaperekond pakub uskumatut 1ns levimisviivitust ja viimastes ECL-perekondades on see viivitus vähenenud. Siin on teile küsimus, mis on ECL-i alternatiivne nimi?