Oma igapäevases elus kasutame me teistega sageli suhtlemiseks, kasutades mitut tüüpi sidesüsteemid . Seda sidesüsteemi saab liigitada erinevat tüüpi, näiteks raadiosidesüsteem, telekommunikatsioonisüsteem, Traadita sidesüsteem , Optiline sidesüsteem jne. Kõigi nende sidesüsteemide tõhusaks toimimiseks vajame mõningaid juhtimissüsteeme, nagu faasilukustatud silmus, ühistu juhtimine, juhtimine võrgus ja nii edasi.

Mis on faasilukustatud ring (PLL)?

Faasilukustatud silmust kasutatakse juhtimissüsteemina erinevate toimingute juhtimiseks paljudes sidesüsteemides, arvutites ja paljudes elektroonilised rakendused . Seda kasutatakse väljundsignaali genereerimiseks, millel on sisendsignaali faasiga seotud faas.

PLL-e on erinevat tüüpi, näiteks Analoog või Lineaarne PLL, Digitaalne PLL, Tarkvara PLL, Neuronaalne PLL ja kõik digitaalsed PLL.

Faasilukustatud kontuur

Sidesüsteemides saab PLL-i toimimist seletada kaalumisega analoog- ja digitaalsüsteemid .

Analoogne faasilukustatud silmus sidesüsteemides

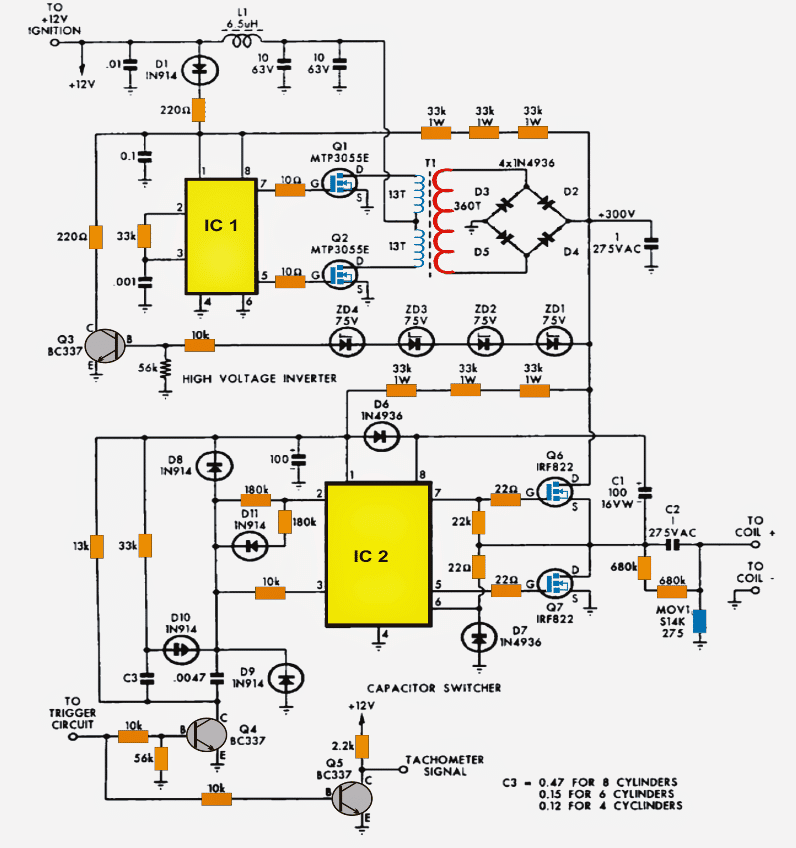

Põhimõtteliselt on PLL servoahela vorm ja põhiline PLL koosneb kolmest põhielemendist, nimelt faaside võrdleja / detektor, silmusfilter ja pingega juhitav ostsillaator .

Faas on lukustatud

PPL-operatsiooni peamine kontseptsioon on kahe signaali faaside võrdlemine (üldiselt võrreldakse sisendi ja väljundi signaali faase). Seega saab sisend- ja väljundsignaali faaside erinevust kasutada silmusageduse juhtimiseks. Kuigi matemaatiline analüüs on väga keeruline, kuid PLL-i toimimine on väga lihtne.

Paljudes sidesüsteemides kasutatakse PLL-i erinevatel eesmärkidel:

- Etapi järgimiseks või sageduse modulatsioon , seda kasutatakse demodulaatorina.

- Kahe erineva sagedusega signaali jälgimiseks või sünkroonimiseks.

- Suurte müra eemaldamiseks pisikestest signaalidest.

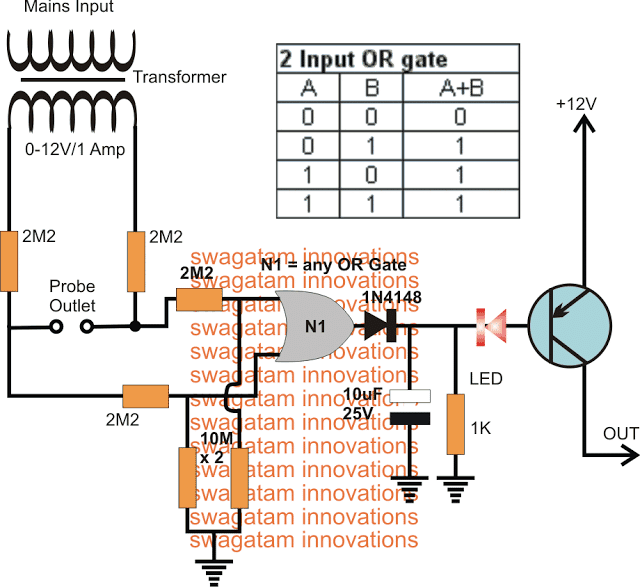

Alloleval joonisel on näidatud põhiline PLL, mis koosneb faasidetektorist, pingega juhitavast ostsillaatorist (VCO), silmusfiltrist.

PLL pingejuhtimisega ostsillaator tekitab signaali ja see VCO signaal antakse faasidetektorile. Faasidetektor võrdleb seda signaali võrdlussignaaliga ja tekitab seega veapinge või erinevuspinge. See faasidetektori veasignaal suunatakse madalpääsfiltrisse signaali kõrgsageduslike elementide eemaldamiseks - kui üldse - ja juhtimissilmu paljude omaduste juhtimiseks. Seejärel suunatakse silmusfiltri väljund pinge abil juhitava ostsillaatori juhtklemmi häälestuspinge andmiseks.

Selle häälestuspinge muutust tajutakse kahe signaali (sisendi ja väljundi) faaside erinevuse ja seega ka nende vahelise sageduse vähendamiseks. Esialgu PLL ei lukustu ja veapinge lohistab VCO sagedust võrdluse suunas, kuni viga ei saa enam vähendada ja siis lukustatakse silmus.

Kahe signaali (sisendi ja väljundi) tegelik viga vähendatakse väga väikesele tasemele võimendi abil pingega juhitava ostsillaatori ja faasidetektori vahel. Kui PLL on lukustatud, tekib püsiva oleku veapinge. See püsiseisundi tõrke pinge näitab, et etalonsignaali ja VCO vahel pole faaside erinevuse muutust. Seega võime öelda, et kahe signaali (sisend- ja väljundsignaal) sagedus on täpselt sama.

Digitaalfaasi lukustatud silmus sidesüsteemides

Üldiselt koosnevad analoog-PLL-id analoogfaasidetektorist, pingega juhitavast ostsillaatorist ja madalpääsfiltrist. Sarnaselt koosneb digitaalse faasi lukustatud silmus digitaalse faasi detektorist a jadavahetuse register , stabiilne - kohaliku kella signaal.

Digitaalfaasi lukustatud silmus

Digitaalse sisendi proovid eraldatakse vastuvõetud signaalist ja need proovid võetakse vastu jada vahetuste registris, mida juhivad kohaliku kella signaalilt edastatud kellimpulsid. Faasikorrektorahelat, mis võtab kohalikku kella, kasutatakse stabiilse kella signaali regenereerimiseks faasis vastuvõetud signaaliga aeglase faasi reguleerimisega, et see vastaks vastuvõetud signaali faasile.

Selle reguleerimise saab teha iga biti kiire valimi põhjal, kasutades parandusloogikat. Kohalikul taktsagedusel vastuvõetud signaali proovivõtuga saadud vastuvõetud signaali proov paigutatakse nihkeregistrisse.

Vajaliku faasi reguleerimise saab tuvastada, vaadeldes vastuvõetud signaali proovide komplekti. Kaks kella on väidetavalt faasilised siis ja ainult siis, kui vastuvõetud biti keskpunkt asub nihkeregistri keskel. Faasiregulaator on ette nähtud kompenseerimiseks, kui regenereeritud kell jääb viitesignaali viivituse või juhib.

Faasilukustatud ahela rakendamine

- PLL-sid kasutatakse sageli sünkroniseerimise eesmärgil ja bittide sünkroniseerimiseks, sümbolite sünkroniseerimiseks, koherentseks demoduleerimiseks ja lävepikenduseks kosmosesuhtluses.

- Sagedusmoduleeritud signaale saab demoduleerida PLL-i abil.

- Uus sagedus, mis on võrdlussageduse korrutis raadioside saatjad ja sünteesitakse võrdlussageduse stabiilsuse säilitamise abil uue sagedusega PLL-de abil.

- PLL-ide jaoks on arvukalt rakendusi paljudes sidesüsteemides, arvutites ja paljudes elektroonilised ahelad .

- Allpool toodud PLL-i rakendus kirjeldab PLL-i kasutamist pingena sageduse konverter .

Pinge-sagedusmuundur (VFC) PLL-i abil

Sidesüsteemides on vaja signaale (arvestage siin analoogsignaaliga) pika vahemaa tagant täieliku täpsusega. Sel eesmärgil kasutatakse pinge-sagedusmuundurit, kuna optiliste isolaatorite, koaksiaalsete või keerdpaarliinide, raadiolinkide, kiudoptilised ühendused .

Pinge-sagedusmuundureid on kahte tüüpi, nimelt multivibraatori tüüp VFC ja laadimissaldo tüüp VFC.

Multivibraatori tüüp VFC

Multivibraator VFC

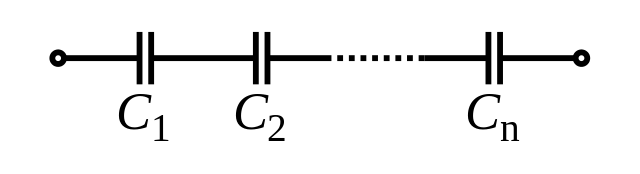

Multivibraatoritüüpi VFC korral laaditakse kondensaator sisendpingest saadud voolu kasutades tühjaks. Stabiilne referentssisend antakse ümberlülitusläve seadmiseks ja väljundsagedus on proportsionaalne sisendpingega ning ühtsuse ja ruumi suhtega.

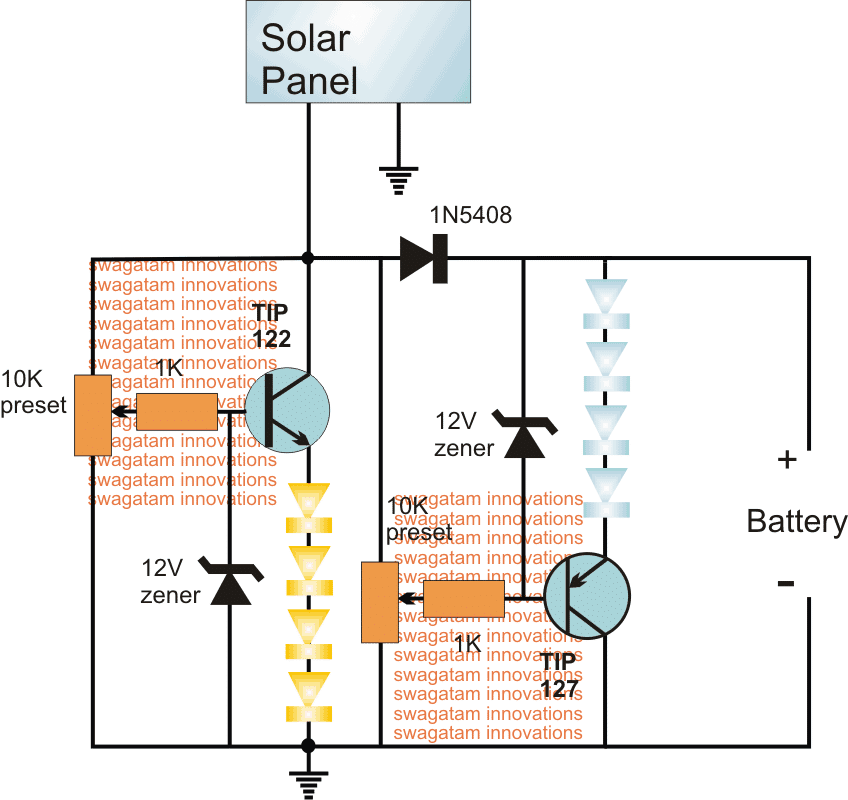

Laadimissaldo tüüp VFC

Laadimise saldo VFC

Laadustasakaal VFC koosneb integraatorist, komparaatorist ja täppislaadimisallikast. Kui integraatorile antakse sisend, laetakse see ja kui selle integraatori väljund jõuab võrdlusläveni, käivitatakse laadimisallikas ja fikseeritakse eemaldatakse integraatorist. Eemaldatud laengu määr peab olema võrdne laetud kiirusega nii, et laadimisallika käivitatav sagedus ja integraatori sisend oleksid üksteisega proportsionaalsed.

Seega annab see artikkel lühikirjelduse faasilukustatud süsteem sidesüsteemis. Seda artiklit saab teie ettepanekute ja päringute põhjal tehniliselt laiendada. Seega võite tehnilise abi saamiseks pöörduda meie poole, postitades oma kommentaarid allpool.