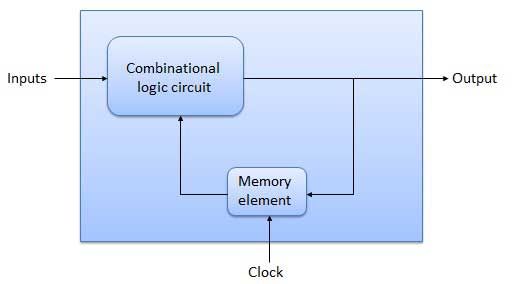

Erinevat tüüpi digitaalsüsteemid on konstrueeritud väga vähestest põhivõrgu konfiguratsioonidest, näiteks AND gate, NAND gate, or gate jne ... Neid elementaarseid vooluringe kasutatakse ikka ja jälle erinevates topoloogilistes kombinatsioonides. Lisaks loogika teostamisele peavad digitaalsed süsteemid salvestama ka binaararvud. Nende mälurakkude, tuntud ka kui PLÄTU' on kavandatud. Mõne funktsiooni täitmiseks, näiteks binaarne liitmine. Seega, selliste funktsioonide täitmiseks, loogika väravad ja FLIP-FLOP-id on loodud üle ühe kiibiga IC. Need IC-d moodustavad digitaalsüsteemide praktilised ehituskivid. Üks sellistest binaarse liitmise komponentidest on Carry Look-forward Adder.

Mis on edasijõudnute eelvaade?

Digitaalarvuti peab sisaldama vooluringe, mis võimaldavad teha aritmeetilisi toiminguid nagu liitmine, lahutamine, korrutamine ja jagamine. Nende hulgas on liitmine ja lahutamine põhilised toimingud, samas kui korrutamine ja jagamine on vastavalt korduv liitmine ja lahutamine.

Nende toimingute teostamiseks rakendatakse põhiloogika väravaid kasutades „liiteahelaid“. Lisaja vooluringid on arenenud kui pool-liider, täis-lisaja, Ripple-carry-lisaja ja Carry Look-forward-lisaja.

Nende Carry Look-forward Adderi hulgas on kiirem lisaahel. See vähendab paljundamise viivitust, mis tekib lisamise ajal, kasutades keerukamaid riistvaralülitusi. Selle eesmärk on muuta pulsse kandva Adderi vooluring nii, et liitja kandeloogika muudetakse kahetasandiliseks.

4-bitine kandepildi lisaja

Paralleelselt liidetuna antakse iga täissummeri kandeväljund kandesisendina järgmisse kõrgema astme olekusse. Seega pole nende liitjate abil võimalik luua ühegi oleku kande- ja väljundväljundeid, kui selle oleku jaoks pole kandesisendit saadaval.

Nii et arvutuse toimumiseks peab vooluring ootama, kuni kandebitt levib kõikidesse olekutesse. See kutsub esile vooluahelas levimise viivituse.

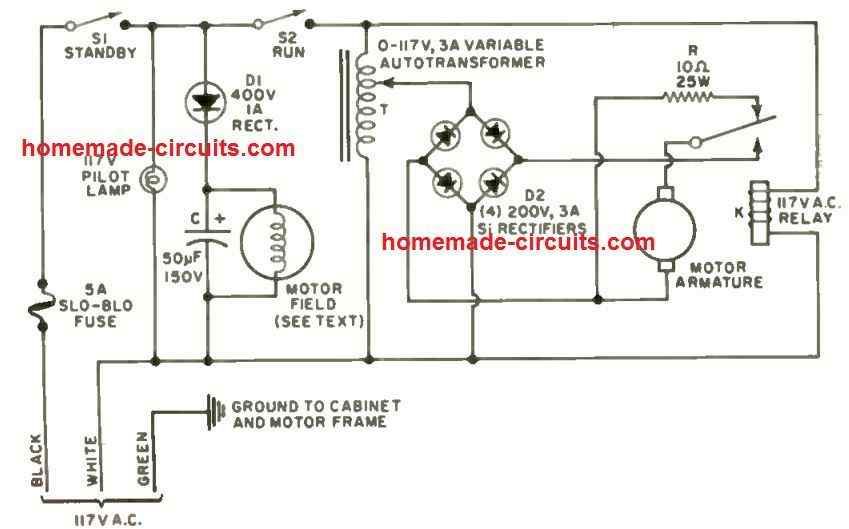

4-bitine Ripple-Carry-Adder

Mõelge ülalolevale 4-bitisele pulsatsioonikanduri liiteahelale. Siin saab summa S3 toota kohe, kui sisendid A3 ja B3 on antud. Kuid kandet C3 ei saa arvutada enne, kui kandebitt C2 on rakendatud, samas kui C2 sõltub C1-st. Seetõttu peab lõplike püsiseisundi tulemuste saamiseks kandmine levima läbi kõigi olekute. See suurendab vooluahela levimise viivitust.

Lisaja leviku viivitus arvutatakse järgmiselt: 'iga värava levimisviivitus korrutab ahela etappide arvu'. Suure hulga bitide arvutamiseks tuleb lisada rohkem etappe, mis muudab viivituse palju hullemaks. Seega võeti selle olukorra lahendamiseks kasutusele Carry Look-forward Adder.

Carry Look-forward Adderi toimimise mõistmiseks kirjeldatakse allpool 4-bitist Carry Look-forward Adderi.

4-bitine-kanna-vaata-ette-lisaja-loogika-skeem

Selles summaeris on summaatori mis tahes astme kandesisend sõltumatu iseseisvatel etappidel genereeritud kandebittidest. Siin sõltub mis tahes etapi väljund ainult eelmistes etappides lisatud bittidest ja algstaadiumis pakutavast kandesisendist. Seega ei pea ükski etapp ahelat ootama eelmise etapi kandebiti genereerimist ja kandebitti saab hinnata igal ajahetkel.

Tõe tabel ülekandvaate lisaja kohta

Selle liitja tõetabeli tuletamiseks on kasutusele võetud kaks uut mõistet - kandmise genereerimine ja leviku kandmine. Kandegeneraator Gi = 1 alati, kui genereeritakse kandevõime Ci + 1. See sõltub Ai ja Bi sisenditest. Gi on 1, kui mõlemad Ai ja Bi on 1. Seega arvutatakse Gi järgmiselt: Gi = Ai. Bi.

Kandega paljundatud Pi on seotud kande levimisega Ci-st Ci + 1-ni. See arvutatakse järgmiselt: Pi = Ai ⊕ Bi. Selle lisaja tõetabeli saab tuletada täissummuti tõetabeli muutmisest.

Kasutades termineid Gi ja Pi, on Sum Si ja Carry Ci + 1 toodud allpool -

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

Seetõttu saab kandebitte C1, C2, C3 ja C4 arvutada järgmiselt

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0). P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1). P2 + G2.

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Seda võrrandit võib täheldada, et Ci + 1 kandmine sõltub ainult kandest C0, mitte vahepealsetest bittidest.

Carry-Look-forward-Adder-Truth-tabel

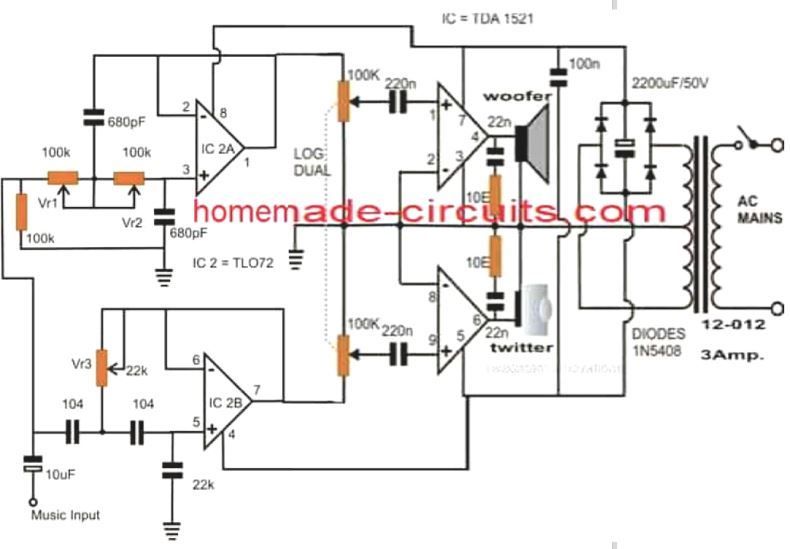

Vooluringi skeem

Eespool toodud võrrandeid rakendatakse kahetasandiliste kombinatsioonahelate abil koos AND, OR väravatega, kus eeldatakse, et väravatel on mitu sisendit.

Carry-Output-Generation-Circuit-of-Carry-Look-forward-Adder

Allpool on toodud Carry Look-forward Adderi vooluring 4-bitiselt.

4-bitine Carry-Look-forward-Adder-vooluringi skeem

8-bitiseid ja 16-bitiseid Carry Look-forward Adderi vooluringe saab kujundada 4-bitise liiteahela kaskaadiga kandmisloogikaga.

Carry Look-forward Adderi eelised

Selles liitmises väheneb levimise viivitus. Kandevõimsus sõltub igal etapil ainult algstaadiumi algsest kandebittist. Selle summaatori abil on võimalik arvutada vahetulemused. See summaer on arvutamiseks kõige kiirem liitja.

Rakendused

Kiireid Carry Look-forward-lisandeid kasutatakse IC-dena rakendatuna. Seega on liitjat ahelatesse lihtne kinnistada. Kahe või enama liitja kombineerimisel saab kõrgemate buutide logifunktsioonide arvutusi hõlpsasti teha. Siin on väravate arvu suurenemine mõõdukas ka siis, kui neid kasutatakse suuremate bitide jaoks.

Selle lisaja jaoks on kompromiss ala ja kiiruse vahel. Suuremate bittarvutuste korral tagab see suure kiiruse, kuid suureneb ka vooluahela keerukus, suurendades seeläbi ahela hõivatud pindala. Seda lisamoodulit rakendatakse tavaliselt 4-bitiste moodulitena, mis on kõrgemate arvutuste tegemisel ühendatud kaskaadiga. See lisaja on teiste lisanditega võrreldes kallim.

Boole'i arvutamiseks arvutites kasutatakse regulaarselt lisaaineid. Charles Babbage rakendas arvutites kandepinna ennetamise mehhanismi, et vähendada pulsatsioonikandjad . Süsteemi kujundamise ajal on arvutamise kiirus disaineri jaoks kõige suurem otsustav tegur. 1957. aastal patenteeris Gerald B. Rosenberger kaasaegse Binary Carry Look-forward Adderi. Värava viivituse ja simulatsiooni analüüsi põhjal viiakse läbi katseid selle summaatori vooluahela modifitseerimiseks, et muuta see veelgi kiiremaks. Kui suur on n-bitise ettenägeva liitmiku korral viivitus, kui iga värava viivitus on 20?

Pildikrediit