Käskude või käskude arhitektuur on arvuti struktuur, mis annab arvutile käske, et suunata arvutit andmetega manipuleerimise töötlemiseks. Juhendikomplekt koosneb käskudest, adresseerimisrežiimidest, algandmetüüpidest, registritest, katkestustest, erandite käsitlemisest ja mäluarhitektuurist. Juhiste komplekti saab tarkvara abil tõlgendada tõlgi abil või sisseehitatud protsessori riistvarasse. Instruktsioonikomplekti arhitektuuri võib pidada piiriks tarkvara ja riistvara vahel. Mikrokontrollerite klassifikatsioon ja mikroprotsessoreid saab teha RISC ja CISC käskude arhitektuuri põhjal.

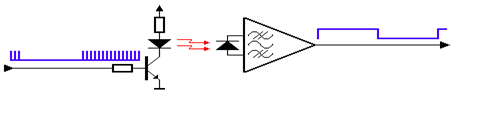

Protsessori juhiste komplekt

Juhiste komplekt määrab protsessori funktsionaalsuse, sealhulgas protsessori toetatavad toimingud, protsessori salvestusmehhanismid ja viisid, kuidas programmid protsessorile kompileerida.

Mis on RISC ja CISC?

The RISC ja CISC saab laiendada järgmiselt:

RISC tähistab vähendatud juhiste komplekti arvutit ja

CISC tähistab keerukat juhiste komplekti arvutit.

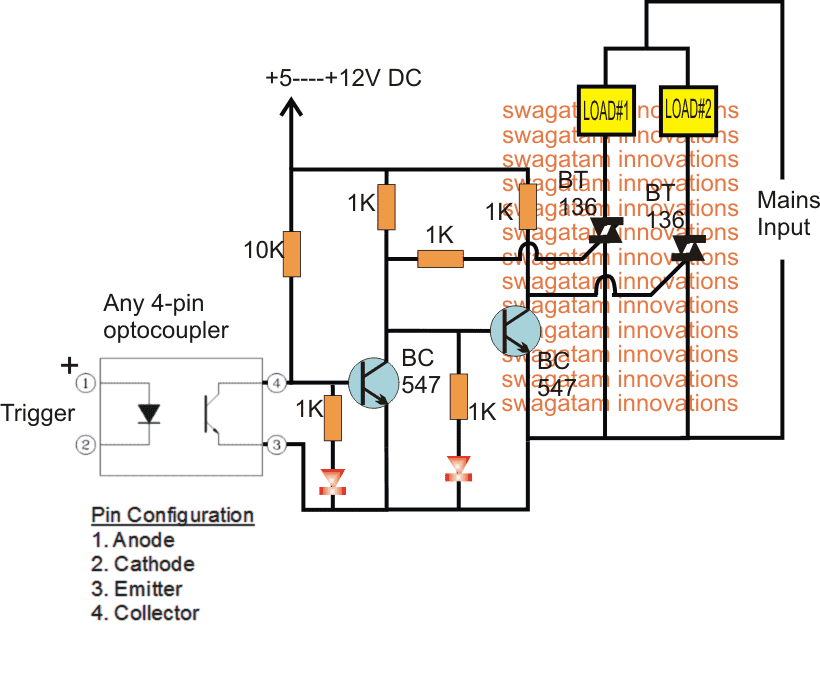

RISC (Reduced Instruction Set Computer) arhitektuur

RISC arhitektuur

The mikrokontrolleri arhitektuur See, mis kasutab väikest ja väga optimeeritud käskude komplekti, nimetatakse vähendatud käsukomplektiks või lihtsalt RISC-ks. Seda nimetatakse ka LOAD / STORE arhitektuuriks.

1970. aastate lõpus ja 1980. aastate alguses töötati RISCi projekte välja peamiselt Stanfordi, UC-Berkley ja IBMi poolt. John Coke IBMi uurimisrühmast arendas RISC-i, vähendades arvutuste töötlemiseks vajalike käskude arvu kiiremini kui CISC. RISC arhitektuur on kiirem ja RISC arhitektuuri valmistamiseks vajalikud kiibid on ka CISC arhitektuuriga võrreldes odavamad.

RISC arhitektuuri tüüpilised omadused

- RISC-i torujuhtmetehnika täidab korraga mitu käsu osa või etappi, nii et kõik protsessori juhised on optimeeritud. Seega on RISC-protsessoritel Clock per Instructions ühes tsüklis ja seda nimetatakse ühe tsükli täitmiseks.

- See optimeerib registri kasutamine kui RISC-s on rohkem registreid ja mälus on rohkem interaktsioone, saab ära hoida.

- Lihtsad adresseerimisrežiimid, isegi keeruka adresseerimise saab teha aritmeetika abil JA / VÕI loogilised toimingud .

- See lihtsustab kompilaatori kujundust, kasutades identseid üldotstarbelisi registreid, mis võimaldab mis tahes registrit kasutada mis tahes kontekstis.

- Registrite tõhusaks kasutamiseks ja torujuhtmete kasutamise optimeerimiseks on vaja väiksemat käskude komplekti.

- Opkoodi jaoks kasutatavate bitide arvu vähendatakse.

- Üldiselt on RISC-s 32 või enam registrit.

RISC protsessori arhitektuuri eelised

- RISC-i väikeste juhiste komplekti tõttu saavad kõrgetasemelised keelekompilaatorid luua tõhusama koodi.

- RISC võimaldab ruumi vaba kasutamist mikroprotsessorid selle lihtsuse tõttu.

- Stacki kasutamise asemel kasutavad paljud RISC-protsessorid registreid argumentide edastamiseks ja kohalike muutujate hoidmiseks.

- RISC-funktsioonid kasutavad ainult mõnda parameetrit ja RISC-protsessorid ei saa kasutada kõnejuhiseid ning seetõttu kasutavad nad fikseeritud pikkusega käske, mida on lihtne juhtida.

- Operatsiooni kiirust saab maksimeerida ja täitmisaega minimeerida.

- Vaja on väga vähe käsuvorminguid (vähem kui neli), mõnda käskude arvu (umbes 150) ja mõnda aadressimisrežiimi (vähem kui neli).

RISC-protsessori arhitektuuri puudused

- Koos käskude pikkuse suurenemisega suureneb RISC-protsessorite käivitamise keerukus tänu oma märkide tsüklile käsu kohta.

- RISC-protsessorite jõudlus sõltub enamasti kompilaatorist või programmeerijast, kuna kompilaatori teadmised mängivad suurt rolli, samal ajal kui CISC-kood teisendatakse RISC-koodiks, sõltub genereeritud koodi kvaliteet kompilaatorist.

- CISC-koodi ajakava muutmine RISC-koodiks, mida nimetatakse koodi laiendamiseks, suurendab suurust. Ja selle koodi laiendamise kvaliteet sõltub jällegi kompilaatorist ja ka masina juhistekomplektist.

- RISC-protsessorite esimese taseme vahemälu on ka RISC-i puuduseks, kuna nende protsessorite kiibil endal on suured mälu vahemälud. Juhiste söötmiseks vajavad nad väga kiired mälusüsteemid .

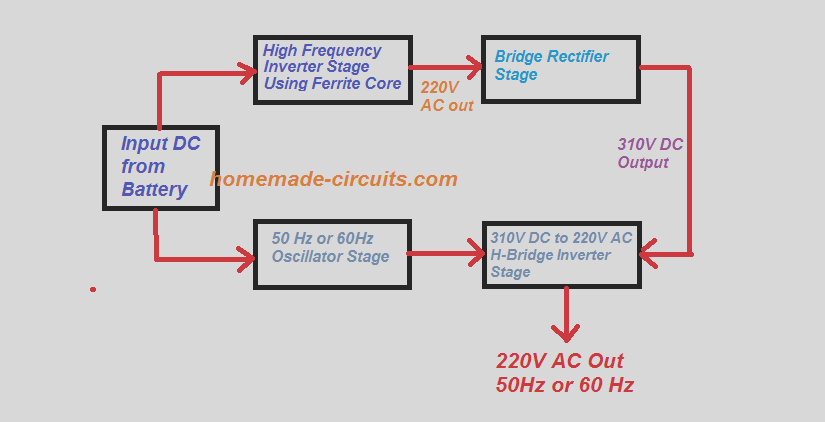

CISC (Complex Instruction Set Computer) arhitektuur

CISC protsessori arhitektuuri peamine eesmärk on täita ülesanne, kasutades vähem konveierliine. Sel eesmärgil on protsessor ehitatud rea toimingute sooritamiseks. Kompleksset juhendamist nimetatakse ka toimivaks MULT mälupangad otse arvuti kompileerijat salvestamis- ja laadimisfunktsioone teostama panemata.

CISC arhitektuur

CISC arhitektuuri omadused

- Arvuti arhitektuuri lihtsustamiseks toetab CISC mikroprogrammeerimist.

- CISC-l on rohkem etteantud juhiseid, mis muudab kõrgetasemelised keeled hõlpsasti kujundatavaks ja juurutatavaks.

- CISC koosneb vähemast registrite arvust ja suuremast adresseerimisrežiimide arvust, tavaliselt 5 kuni 20.

- CISC-protsessor võtab käskude täitmiseks erineva tsükliaja - mitme kella tsüklid.

- CISC keeruka käskude komplekti tõttu on torujuhtmete tehnika väga keeruline.

- CISC koosneb suuremast arvust juhistest, tavaliselt 100 kuni 250.

- Erijuhiseid kasutatakse väga harva.

- Mälus olevaid operante manipuleeritakse juhistega.

CISC arhitektuuri eelised

- Iga masinakeelekäsk on rühmitatud mikrokoodi käskudeks ja täidetud vastavalt sellele ning seejärel salvestatakse peaprotsessori mällu sisseehitatud kujul, mida nimetatakse mikrokoodi rakenduseks.

- Kuna mikrokoodimälu on kiirem kui põhimälu, saab mikrokoodi käskude komplekti rakendada ilma traadita rakenduse kiiruse märkimisväärse vähendamiseta.

- Mikroprogrammi kujunduse muutmisega saab hakkama kogu uue käskudega.

- CISC-s saab programmi rakendamiseks vajalike käskude arvu vähendada rikkalike käskude kogumite loomisega ja panna ka aeglast põhimälu tõhusamalt kasutama.

- Kõigist varasematest käskudest koosneva käsukomplekti tõttu muudab see mikrokodeerimise lihtsaks.

CISC puudused

- Erinevate juhiste järgi kuluv kellaaeg on erinev - seetõttu - masina jõudlus aeglustub.

- Käskude kompleksi keerukus ja kiibi riistvara suureneb, kuna iga uus protsessori versioon koosneb varasemate põlvkondade alamhulgast.

- Ainult 20% olemasolevatest käskudest kasutatakse tüüpilises programmeerimisürituses, kuigi on olemas palju spetsiaalseid juhiseid, mida isegi ei kasutata sageli.

- Tingimuslikud koodid määratakse CISC-i käskude abil iga käsu kõrvalmõjuna, mis võtab selle sätte jaoks aega - ja kui järgmine käsk muudab tingimuskoodi bitti, peab kompilaator enne selle juhtumist tingimuskoodi bitti uurima.

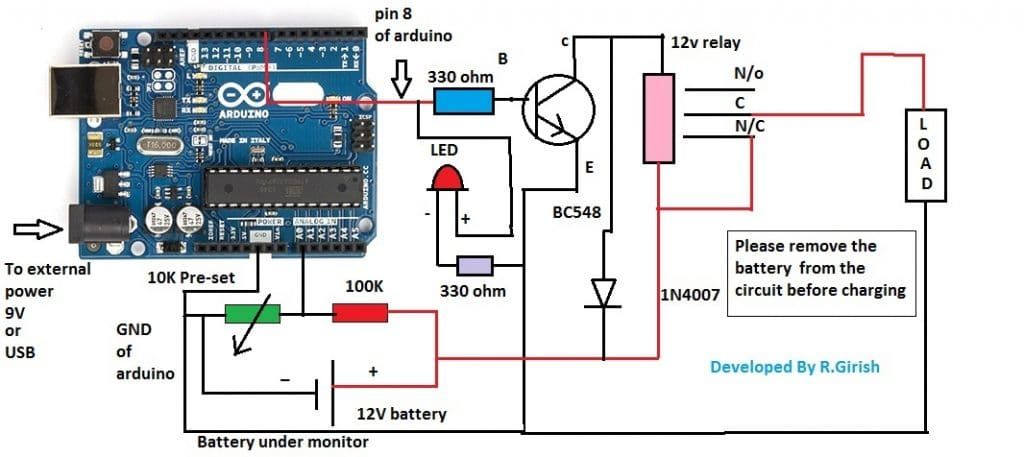

RISC vs. CISC

- Programmeerija saab ära hoida raiskamistsükleid, eemaldades tarbetu koodi RISC-st, kuid CISC-koodi kasutamine viib CISC-i ebaefektiivsuse tõttu raiskamistsükliteni.

- RISC-s on iga käsk mõeldud väikese ülesande täitmiseks, nii et keeruka ülesande täitmiseks kasutatakse koos mitut väikest käsku, samas kui sama ülesande tegemiseks CISC-i abil on vaja ainult mõnda käsku - kuna see on võimeline keeruka ülesande täitmiseks kuna juhised sarnanevad kõrgkeelse koodiga.

- CISC-d kasutatakse tavaliselt arvutite jaoks, RISC-i aga nutitelefonide, tahvelarvutite ja muude elektroonikaseadmete jaoks.

Järgmine joonis näitab rohkem erinevusi RISC ja CISC vahel

RISC vs. CISC

Seega käsitletakse selles artiklis RISC ja CISC arhitektuuride omadusi RISC ja CISC protsessorite arhitektuuri eeliste ja puuduste ning RISC ja CISC arhitektuuride vaheliste erinevuste kohta lühikese ideega. RISC ja CISC arhitektuuri kohta lisateabe saamiseks saatke oma päringud allpool kommenteerides.

Foto autorid:

- Protsessori juhiste kogum arstechnica

- RISC arhitektuur lsi-võistlus

- RISC vs CISC poolt csar määramine