Selles postituses õpime, kuidas luua diskreetsete transistorite abil NOT, AND, NAND, OR ja NOR loogikaväravaid. Transistor-loogikaväravate kasutamise peamine eelis on see, et need võivad töötada isegi nii madala pingega kui 1,5 V.

Mõnes elektroonilises rakenduses võib saadaolev pinge olla TTL-i või isegi CMOS-i IC-de toiteks ebapiisav. See kehtib eriti akudega töötavate vidinate kohta. Kahtlemata on teil alati 3-voldine loogika-IC valik. Kuid need ei ole alati entusiastile või katsetajale kergesti ligipääsetavad ja need ei tööta alla nende määratletud pingespetsifikatsioonide (tavaliselt alla 2,5 volti alalisvoolu).

Lisaks võib akutoitega rakenduses olla koht ainult ühele 1,5-voldise aku jaoks. No mida sa siis tegema hakkad? Tavaliselt IC loogika väravad võiks asendada transistoriseeritud loogikaväravatega. Iga konkreetse loogikavärava jaoks on tavaliselt vaja vaid paari transistorit ja tüüpilise NOT-gate inverteri loogika jaoks on vaja ainult ühte transistorit.

FETid versus bipolaarne transistor

Väljatransistorid (FET) vs bipolaarsed transistorid : milline on parem valik madalpinge loogikaahelate jaoks? Üks suurepärane omadus FAKTID on see, et nende 'sisselülitamise' takistus on uskumatult madal. Lisaks vajavad nad väga madalat sisselülitusvoolu.

Siiski on neil üks piirang äärmiselt madala pingega rakendustes. Tavaliselt on paisupinge piirväärtus üks volt või nii. Lisaks võib saadaolev pinge langeda alla FET-i optimaalse tööpiirkonna, kui paisule on kinnitatud voolu piirav või allatõmmatav takisti.

Seevastu bipolaarsete lülitustransistoride eelised on äärmiselt madala pingega ühe akuga rakendustes, kuna nende sisselülitamiseks on vaja ainult 0,6–0,7 volti.

Lisaks on enamik tavalisi FET-e, mida lähimas elektroonikapoes tavaliselt mullpakendites müüakse, sageli kallimad kui bipolaarsed transistorid. Samuti sai üldjuhul osta bipolaarsete transistorite hulgipaketi paari FET-i hinna eest.

FET-i käsitsemine nõuab oluliselt rohkem hoolt kui bipolaarse transistori käsitsemine. Elektrostaatiline ja üldine eksperimentaalne väärkasutus muudavad FET-id kahjustuste suhtes eriti vastuvõtlikuks. Põlenud komponendid võivad rikkuda nauditava, loomingulise katsetamise või uuenduste õhtu, unustamata silumisega kaasnevat emotsionaalset valu.

Transistoride lülitamise põhitõed

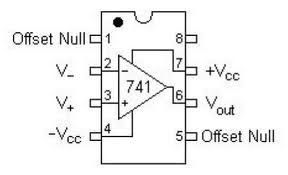

Selles artiklis kirjeldatud loogikalülituste näited kasutavad bipolaarseid NPN-transistore, kuna need on taskukohased ja ei vaja erilist käsitsemist. Seadme või seda toetavate osade kahjustamise vältimiseks tuleks enne vooluringi ühendamist võtta kasutusele sobivad ohutusmeetmed.

Kuigi meie ahelad on peamiselt keskendunud bipolaarsetele ristmiktransistoridele (BJT), oleks neid võinud sama hästi ehitada ka FET-tehnoloogia abil.

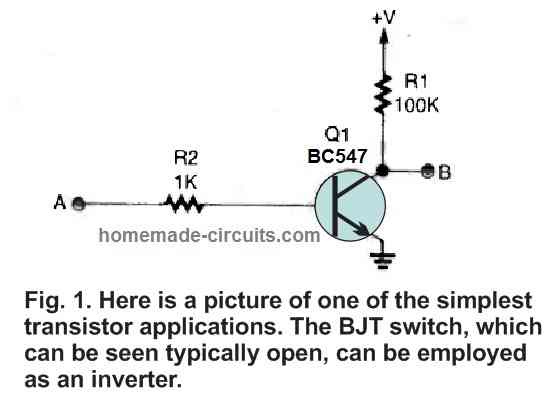

Põhilüliti on lihtne transistorirakendus, mis on üks lihtsamaid konstruktsioone.

NOT-värava valmistamine ühe transistoriga

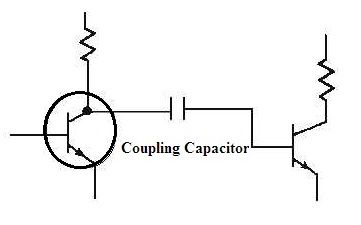

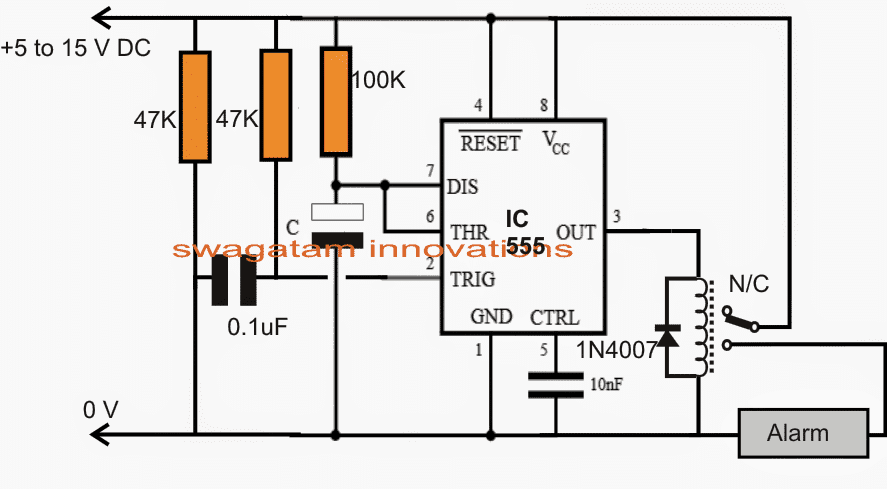

Transistorlüliti skemaatiline skeem on näidatud joonisel 1. Sõltuvalt sellest, kuidas see konkreetses rakenduses on rakendatud, võib lülitit vaadelda kas madalal hoituna või normaalselt avatud.

Lihtsa EI-värava inverteri loogikavärava saab luua joonisel 1 näidatud lihtsa lülitusahelaga (kus punkt A on sisend). NOT-värav töötab nii, et kui transistori baasi (punkt A; Q1) ei anta alalispinget, jääb see väljalülitatuks, mille tulemuseks on kõrge või loogiline 1 (võrdne V+ tasemega) väljundis ( punkt B).

Transistor aktiveerub aga siis, kui Q1 baasile antakse õige eelpinge, mis surub ahela väljundi madalale või loogikale 0 (peaaegu võrdne nullpotentsiaaliga). Transistor, tähisega Q1, on üldotstarbeline bipolaarne transistor või BC547, mida kasutatakse tavaliselt väikese võimsusega lülitus- ja võimendirakendustes.

Kõik sellega võrdväärsed transistorid (näiteks 2N2222, 2N4401 jne) töötaksid. R1 ja R2 väärtused valiti selleks, et leida kompromiss madala voolu äravoolu ja ühilduvuse vahel. Kõigis konstruktsioonides on takistid kõik 1/4 vatti, 5% ühikut.

Toitepinge on reguleeritav vahemikus 1,4 kuni 6 volti alalisvoolu. Pange tähele, et vooluahel võib töötada puhvrina, kui koormustakisti ja väljundühendus on nihutatud transistori emitterile.

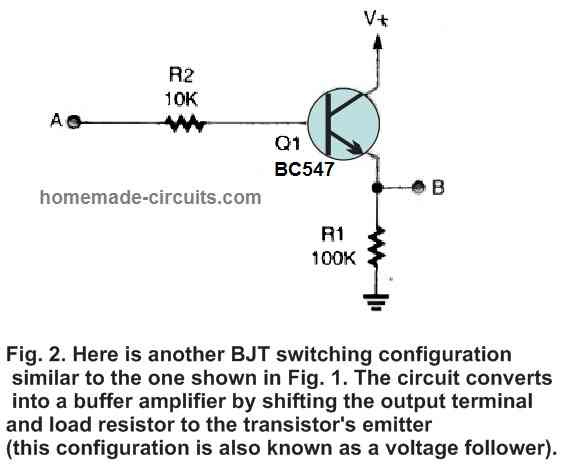

Puhvervärava valmistamine ühe BC547 BJT abil

Pingejärgija ehk puhvervõimendi on loogilise lülituskonfiguratsiooni tüüp, mis on identne joonisel 2 kujutatuga. Tuleb märkida, et koormustakisti ja väljundklemm on selles ahelas nihutatud transistori kollektorilt selle emitterile, mis on peamine erinevus selle disaini ja joonisel 1 kujutatu vahel.

Transistori toimimist saab ka 'pöörata', liigutades koormustakisti ja väljundklemmi BJT teise otsa.

Teisisõnu, kui ahela sisendile ei anta eelpinget, jääb ahela väljund madalaks; aga kui ahela sisendisse antakse piisava pinge eelpinge, muutub ahela väljund kõrgeks. (See on täpselt vastupidine varasemale vooluringile.)

Kahe sisendiga loogikaväravate projekteerimine transistoride abil

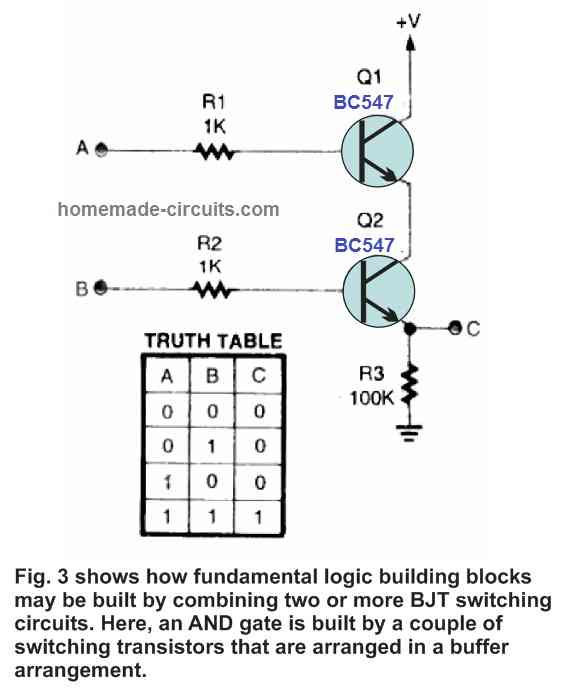

JA värav, kasutades kahte transistori

Joonis 3 illustreerib, kuidas saab puhvripaari kasutades luua põhilise kahesisendilise JA-värava koos selle värava tõesuse tabeliga. Tõelisuse tabel illustreerib, millised oleksid väljundtulemused iga erineva sisendikomplekti puhul. Punkte A ja B kasutatakse vooluringi sisenditena ning punkti C toimib ahela väljundina.

Tõetabelist on oluline märkida, et ainult üks sisendparameetrite komplekt annab loogiliselt kõrge väljundsignaali, samas kui kõigi teiste sisendkombinatsioonide tulemuseks on loogiliselt madala väljundsignaal. AND-värava väljund joonisel 3 jääb veidi alla V+, kui see muutub kõrgeks.

See juhtub kahe transistori (Q1 ja Q2) vahelise pingelanguse tõttu.

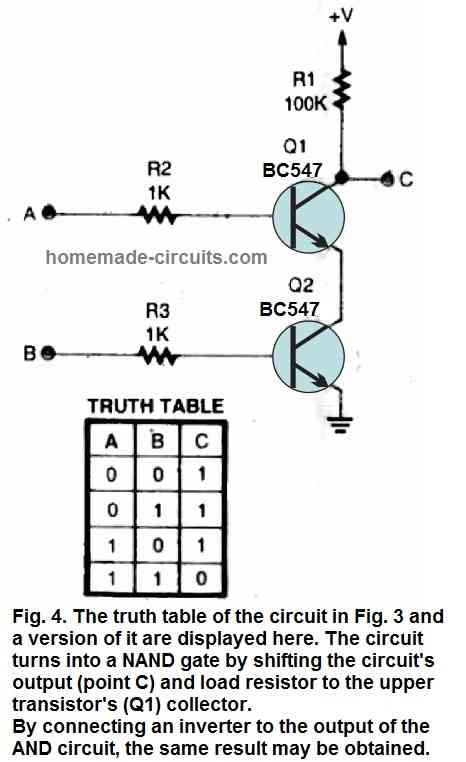

NAND-värav, kasutades kahte transistori

Joonisel 3 kujutatud ahela teine variant ja sellega seotud tõesuse tabel on näidatud joonisel 4. Ahel muutub NAND-väravaks, nihutades väljundi (punkt C) ja väljundtakisti ülemise transistori (Q1) kollektorisse.

Kuna nii Q1 kui ka Q2 tuleb R1 madala külje maapinnale tõmbamiseks sisse lülitada, on pingekadu väljundis C ebaoluline.

Kui transistori JA või transistori NAND väravad vajavad rohkem kui kahte sisendit, võib näidatud konstruktsioonides ühendada rohkem transistore, et saada kolm, neli jne sisendit JA või NAND väravat.

Kuid üksikute transistoride pingekadude kompenseerimiseks tuleks V+ vastavalt suurendada.

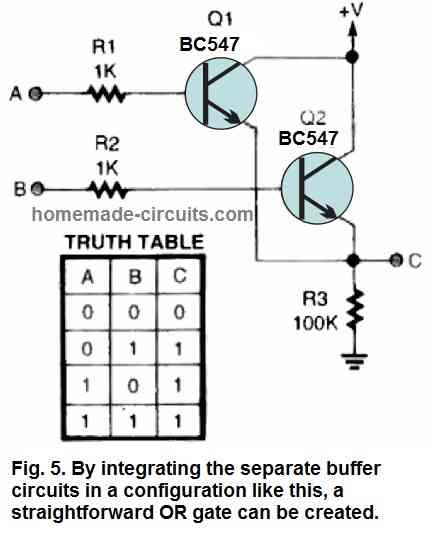

VÕI värav, kasutades kahte transistori

Veel üks kahe sisendiga loogikalülituse vorm on näha joonisel 5 koos VÕI-värava ahela tõesuse tabeliga.

Ahela väljund on kõrge, kui sisend A või sisend B kõrgele lükata, kuid kaskaadtransistoride tõttu on pingelang üle 0,5 volti. Jällegi näitavad kuvatavad arvud, et järgmise transistori paisu jaoks on piisavalt pinget ja voolu.

NOR Gate kasutab kahte transistori

Joonisel 6 on kujutatud meie loendi järgmine värav, kahesisendiline NOR-värav, koos selle tõesuse tabeliga. Sarnaselt sellele, kuidas JA ja NAND väravad üksteisele reageerivad, teevad VÕI ja NOR ahelad sama.

Iga kuvatav värav on võimeline andma piisavalt draivi, et aktiveerida vähemalt üks või mitu külgnevat transistorväravat.

Transistori loogikavärava rakendused

Mida teete ülaltoodud digitaalsete vooluahelatega, mis teil praegu on? Kõik, mida saate saavutada tavaliste TTL- või CMOS-väravatega, kuid ilma toitepingepiirangute pärast muretsemata. Siin on mõned transistor-loogika väravate rakendused.

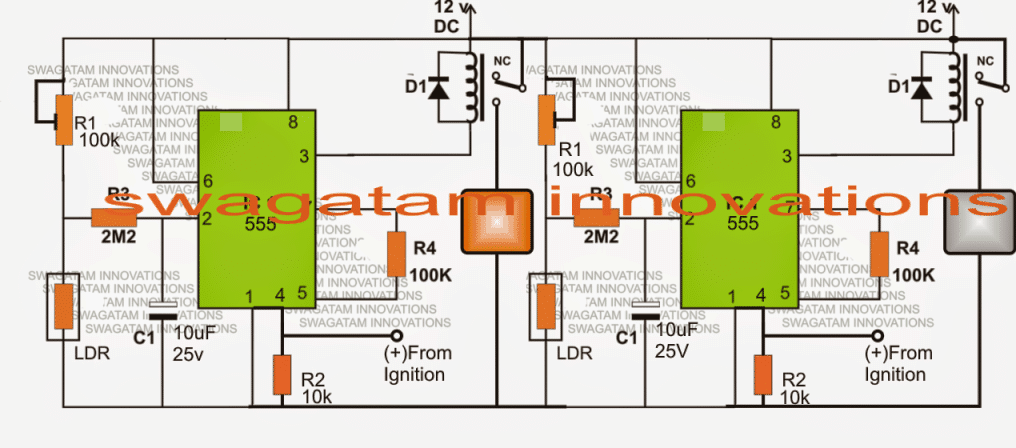

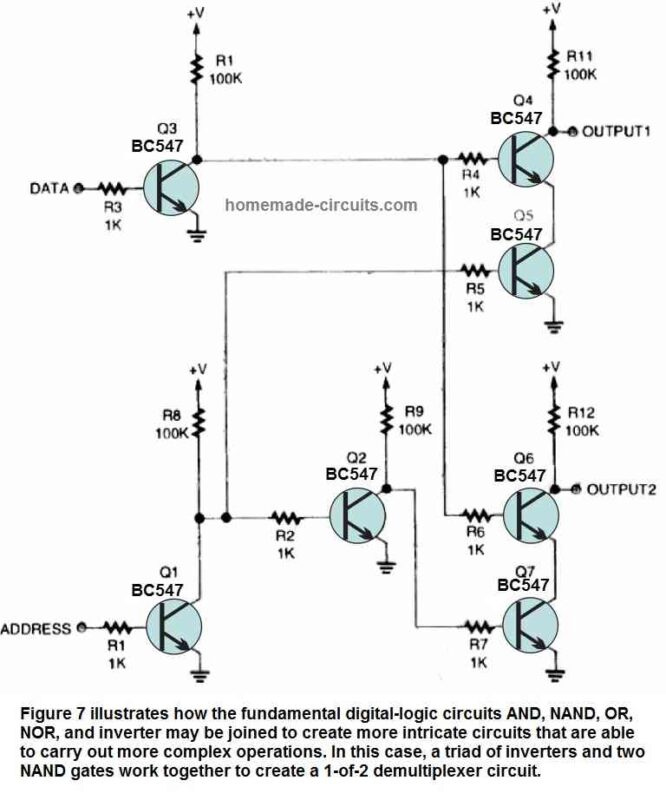

Demultiplekseri vooluahel

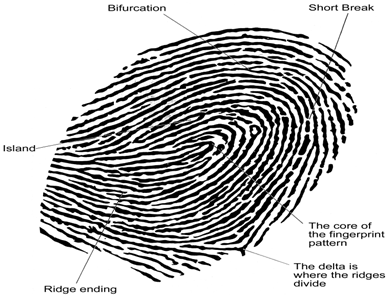

Üks kahest demultiplekser kolme NOT-värava ja kahe NAND-ahelaga on näidatud joonisel 7. Sobiv väljund valitakse ühebitise 'aadressi sisendi' abil, mis võib olla kas OUTPUT1 või OUTPUT2, samal ajal kui sõiduteavet rakendatakse ahelasse, kasutades DATA sisendit.

Ahel töötab kõige tõhusamalt, kui andmeedastuskiirus on alla 10 kHz. Ahela funktsionaalsus on lihtne. DATA sisendit varustatakse vajaliku signaaliga, mis lülitab Q3 ON ja inverteerib sissetulevad andmed Q3 kollektorisse.

Q1 väljund juhitakse kõrgele, kui ADDRESS-sisend on madal (maandatud või signaali ei anta). Q1 kollektoris on kõrge väljund jagatud kaheks teeks. Esimesel teel suunatakse Q1 väljund Q5 baasi (üks kahesisendilise NAND-värava jalgadest), lülitades selle sisse ja seega 'aktiveerides' Q4-st ja Q5-st koosneva NAND-värava.

Teisel teel suunatakse Q1 kõrge väljund samaaegselt teise EI-värava (Q2) sisendisse. Pärast kahekordse inversiooni läbimist muutub Q2 väljund madalaks. See madal on varustatud Q7 baasiga (teise NAND-värava üks klemm, mis koosneb Q6-st ja Q7-st), lülitades seega NAND-ahela välja.

Kõik andmed või signaal, mis on rakendatud DATA-sisendile, jõuab sellistel tingimustel OUTPUT1-sse. Teise võimalusena on olukord vastupidine, kui sisendile ADDRESS antakse kõrge signaal. See tähendab, et kogu vooluringile edastatav teave kuvatakse VÄLJUNDIS 2, kuna Q4/Q5 NAND-värav on keelatud ja Q6/Q7 NAND-värav on lubatud.

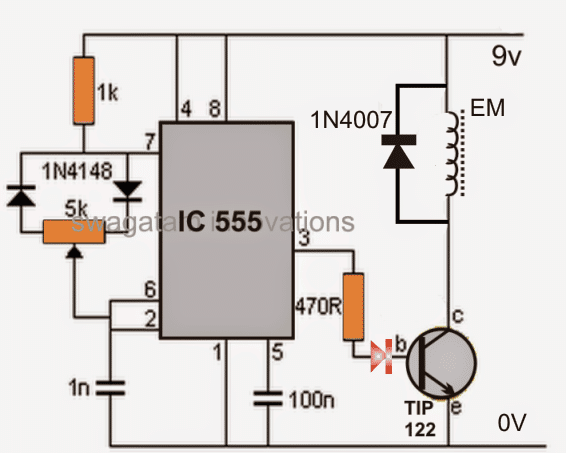

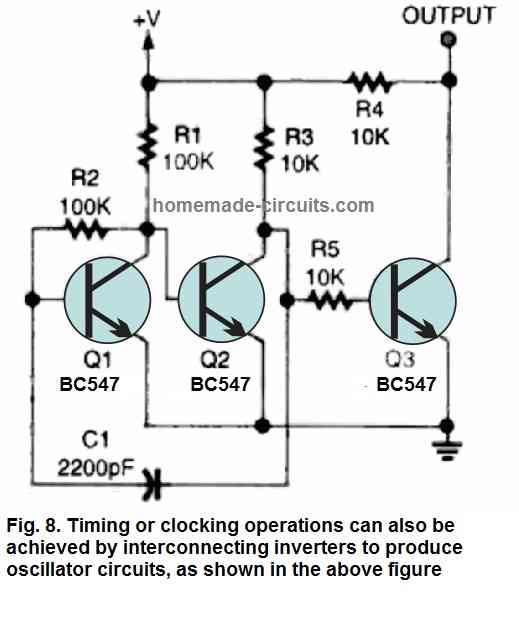

Ostsillaatori ahel (kellageneraator)

Meie järgmine transistori loogikavärava rakendus, mida on illustreeritud joonisel 8, on põhiline kellageneraator (tuntud ka kui ostsillaator), mis on valmistatud kolmest tavalisest NOT-värava inverterist (millest üks on eelpingestatud tagasisidetakisti R2 abil, mis paneb selle analoogpiirkond).

Väljundi ruudustamiseks on kaasas kolmas NOT värav (Q3), mis edastab ostsillaatori väljundi täienduse. Ahela töösageduse muutmiseks saab C1 väärtust suurendada või vähendada. Väljundlainekuju sagedus on umbes 7 kHz V+ juures 1,5 V alalisvoolu juures, kasutades näidatud komponentide väärtusi.

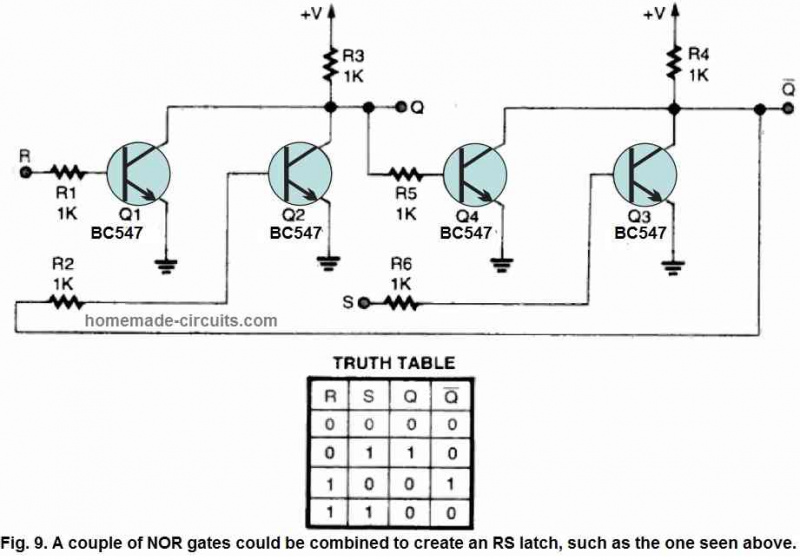

RS lukustusahel

Joonis 9 näitab meie lõplikku rakendusahelat, RS-riivi, mis koosneb kahest NOR-väravast. Tervisliku väljundajami tagamiseks Q ja Q väljunditel on takistid R3 ja R4 reguleeritud 1k oomile.

RS-riivi tõetabel kuvatakse skemaatilise kujunduse kõrval. Need on vaid mõned näited mitmest usaldusväärsest madalpinge digitaalsest loogikavärava ahelast, mida saab luua üksikute transistoride abil.

Transistoriseeritud loogikat kasutavad vooluringid vajavad liiga palju osi

Paljusid probleeme saab lahendada kõigi nende madalpinge transistoriseeritud loogikaahelate abil. Kuid nende transistoriseeritud väravate liiga paljude kasutamine võib põhjustada uusi probleeme.

Transistoride ja takistite arv võib muutuda üsna suureks, kui teie ehitatav rakendus sisaldab palju väravaid, mis hõivavad väärtuslikku ruumi.

Üks võimalus selle probleemi lahendamiseks on kasutada transistori massiive (paljud transistorid on suletud plastikusse) ja SIP (Single Inline Package) takistite kasutamine üksikute üksuste asemel.

Ülaltoodud lähenemisviis võib säästa trükkplaadil tonni ruumi, säilitades samal ajal nende täissuuruses ekvivalentide jõudluse. Transistori massiive pakutakse pindkinnitusega, 14 kontaktiga läbiva avaga ja neljapakendis pakendis.

Enamiku ahelate jaoks võib transistoritüüpide segamine olla üsna vastuvõetav.

Sellegipoolest on soovitav, et eksperimenteerija töötaks transistoriseeritud loogikaahelate koostamiseks ühte tüüpi transistoriga (see tähendab, et kui loote väravast osa BC547 abil, siis proovige kasutada sama BJT-d ka ülejäänud ülejäänud väravate tegemiseks).

Põhjus on selles, et erinevatel transistoride variantidel võivad olla mõnevõrra erinevad omadused ja seega võivad nad käituda erinevalt.

Näiteks mõne transistori puhul võib põhi sisselülitamise piir olla suurem või väiksem kui teisel või võib olla üldine vooluvõimendus, mis on veidi suurem või väiksem.

Teisest küljest võiks üht tüüpi transistori hulgikarbi ostmise hind olla ka väiksem. Teie vooluahelate jõudlus paraneb, kui teie loogikaväravad on ehitatud sobivate transistorite abil ja projekt tervikuna on lõppkokkuvõttes tasuvam.