JTAG (Joint Test Action Group) on väljakujunenud IEEE 1149.1 standard, mis töötati välja 1980. aastal, et lahendada elektrooniliste plaatide või plaatide tootmisprobleeme. trükkplaadid . Seda tehnoloogiat kasutatakse piisava testjuurdepääsu pakkumiseks igale keerukale plaadile, kui testjuurdepääs vähenes. Seega käivitati piiride skaneerimise tehnoloogia & JTAG standard või JTAG spetsifikatsioon on asutatud. Elektroonika keerukus on iga päevaga kasvanud, nii et JTAG-i spetsifikatsioonist on saanud keerukate ja kompaktsete elektroonikaseadmete testimiseks aktsepteeritud testivorming. Selles artiklis käsitletakse ülevaadet a JTAG protokoll – rakendustega töötamine.

Mis on JTAG?

IEEE 1149.1 standardse testipääsupordi ja piiride skaneerimise arhitektuuri nimetus on tuntud kui JTAG (Joint Test Action Group). Seda piirikontrolli arhitektuuri kasutatakse enamasti arvutis protsessorid sest Intel andis välja esimese JTAG-iga protsessori. See IEEE standard lihtsalt määratleb, kuidas arvuti vooluringi testitakse, et teha kindlaks, kas see töötab pärast tootmisprotseduuri õigesti. Trükkplaatidel tehakse katsed jooteühenduste kontrollimiseks.

Joint Test Action Group pakub iga IC-padjaga testijatele nööpnõelte vaadet, mis aitab tuvastada trükkplaadil esinevaid vigu. Kui see protokoll on kiibiga liidestatud, saab see kiibile kinnitada sondi, võimaldades arendajal juhtida nii kiipi kui ka selle ühendusi teiste kiipidega. Liidest Joint Test Action rühmaga saavad arendajad kasutada ka püsivara kopeerimiseks elektroonilise seadme püsimällu.

Konfigureerimine/Pin Out

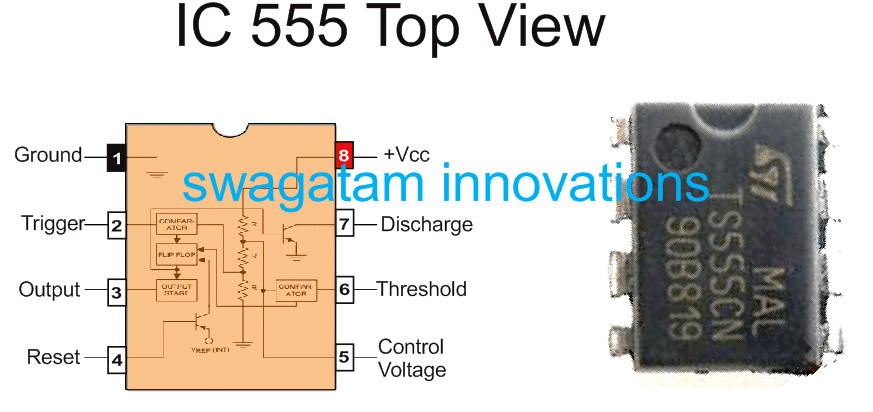

Ühine katserühm sisaldab 20 tihvti, mille iga tihvti ja selle funktsiooni käsitletakse allpool.

Pin1 (VTref): See on sihtmärgi võrdluspinge kontakt, mida kasutatakse sihtmärgi peamise toiteallikaga ühendamiseks, mis jääb vahemikku 1,5–5,0 VDC.

Pin2 (Vsupply): See on sihttoitepinge, mida kasutatakse sihtvõrgu 1,5–5,0 V alalisvoolu peamise toiteallika ühendamiseks.

Pin3 (nTRST): See on test lähtestamise tihvt, mida kasutatakse TAP-kontrolleri olekumasina lähtestamiseks.

Nööpnõelad (4, 6, 8, 10, 12, 14, 16, 18 ja 20): Need on tavalised GND kontaktid.

Pin5 (TDI): See on tihvti testimisandmed. Need andmed nihutatakse sihtseadmesse. See tihvt tuleb sihtplaadil kindlaksmääratud tingimusel üles tõmmata.

Pin7 (TMS): See on testrežiimi oleku viik, mis tõmmatakse TAP-kontrolleri olekumasina järgmise seisundi määramiseks.

Pin9 (TCK): See on testkella tihvt, mis sünkroonib sisemise olekumasina toiminguid TAP-kontrolleris.

Pin11 (RTCK): See on Input Return TCK pin, mida kasutatakse adaptiivset kellaaega toetavates seadmetes.

Pin13 (TDO): See on Test Data Out pin, nii et andmed teisaldatakse sihtseadmest Flyswatterisse.

Pin15 (nSRST): See on Target System Reset viik, mis on ühendatud sihtmärgi põhilähtestussignaaliga.

Tihvtid 17 ja 19 (NC): Need ei ole ühendatud kontaktid.

JTAG töötab

JTAGi algne kasutusala on piiride testimiseks. Siin on lihtne trükkplaat, mis sisaldab kahte IC-d, nagu CPU ja FPGA . Tüüpiline plaat võib sisaldada palju IC-sid. Üldiselt sisaldavad IC-d palju kontakte, mis on ühendatud paljude ühendustega. Siin, järgmisel diagrammil, on näidatud ainult neli ühendust.

Nii et kui kujundate palju tahvleid, kus igal plaadil on tuhandeid ühendusi. Selles on mõned halvad lauad. Seega peame kontrollima, milline plaat töötab ja milline mitte. Selleks loodi ühine katserühm.

See protokoll võib kasutada kõigi kiipide juhttihvte, kuid järgmisel diagrammil loob Joint Test Action Group kõik protsessori väljundviigud ja kõik FPGA sisendviigud. Pärast seda, edastades protsessori viigudest teatud hulga andmeid ja lugedes FPGA-lt kontaktide väärtusi, teatab JTAG, et PCB plaadi ühendused on korras.

Tegelikult sisaldab ühine katserühm nelja loogikasignaali TDI, TDO, TMS ja TCK. Ja need signaalid tuleb teatud viisil ühendada. Alguses on TMS ja TCK ühendatud paralleelselt kõigi JTAG-i IC-dega.

Pärast seda ühendatakse nii TDI kui ka TDO keti moodustamiseks. Nagu näete, sisaldab iga JTAG-iga ühilduv IC 4-viiku, mida kasutatakse JTAG-i jaoks, kus 3-viigud on sisendid ja 4-viik on väljund. Viies tihvt, nagu TRST, on valikuline. Tavaliselt ei jagata JTAG-i kontakte muudel eesmärkidel.

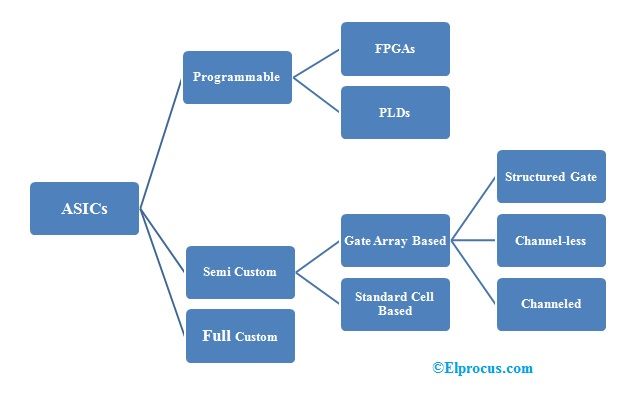

Ühise testimisrühma kasutades kasutavad kõik IC-d piiritesti, mille algse põhjuse on loonud JTAG. Praegu on selle protokolli kasutamist laiendatud, et võimaldada erinevaid asju, nagu FPGA-de konfigureerimine ja pärast seda kasutatakse JTAG-i FPGA tuumas silumiseks.

JTAG arhitektuur

JTAG-i arhitektuur on näidatud allpool. Selles arhitektuuris katkestatakse kõik seadme põhiloogika ja tihvtide vahelised signaalid BSR-i või piiride skaneerimise registri kaudu. See BSR sisaldab erinevaid piiride skaneerimise rakke. Üldiselt ei ole need piiriskannimise lahtrid nähtavad, kuid neid saab kasutada testrežiimis väärtuste seadmiseks või lugemiseks seadme kontaktidest.

JTAG-liides, mida nimetatakse TAP-iks või testpääsupordiks, kasutab piiride skaneerimise toetamiseks erinevaid signaale, nagu TCK, TMS, TDI, TDO ja TRST.

- TCK või Test Clock signaal sünkroniseerib lihtsalt olekusmasina sisetoimingud.

- TMS-i või testrežiimi valimise signaali diskreetimine toimub järgmise oleku otsustamiseks testkella signaali kasvavas servas.

- TDI või Test Data In signaal tähistab nihutatud andmeid testseadmesse, muidu programmeerimisloogika. Kui siseolekumasin on õiges olekus, võetakse selle proovivõtt TCK kasvavast servast.

- TDO või Test Data Out signaal tähistab testseadme muul viisil programmeerimisloogika nihutatud andmeid. Kui siseolekumasin on õiges olekus, kehtib see TCK kahanevas servas

- TRST või Test Reset on valikuline tihvt, mida kasutatakse TAP-kontrolleri olekumasina lähtestamiseks.

TAP-kontroller

JTAG-i arhitektuuri testpöörduspunkt koosneb TAP-kontrollerist, käsuregistrist ja testandmete registritest. See kontroller sisaldab testimisoleku masinat, mis vastutab TMS-i ja TCK-signaalide lugemise eest. Siin kasutatakse andmete i/p viiku lihtsalt andmete laadimiseks IC-südamiku ja füüsiliste kontaktide vahel asuvatesse piirlahtritesse ning andmete laadimiseks ühte andmeregistrisse või käsuregistrisse. Andmete o/p kontakti kasutatakse andmete lugemiseks kas registritest või piirdelahtritest.

TAP-kontrolleri olekumasinat juhib TMS ja seda ajab TCK. Olekumasin kasutab kahe erineva režiimi (nt käsurežiim ja andmerežiim) tähistamiseks kahte teed.

Registrid

Piirikontrollis on saadaval kahte tüüpi registreid. Iga ühilduv seade sisaldab vähemalt kahte andmeregistrit ja ühte käsuregistrit.

Juhendi register

Käskude registrit kasutatakse jooksva käsu hoidmiseks. Seega kasutab TAP-kontroller selle andmeid, et otsustada, mida saadud signaalidega käivitada. Kõige sagedamini kirjeldavad käsuregistri andmed, millisesse andmeregistrisse tuleb signaale edastada.

Andmeregistrid

Andmeregistrid on saadaval kolme tüüpi: BSR (Boundary Scan Register), BYPASS ja ID KOODIDE register. Lisaks võivad seal olla ka muud andmeregistrid, kuid need pole JTAG standardi elemendina vajalikud.

Piiride skaneerimise register (BSR)

BSR on peamine testimisandmete register, mida kasutatakse andmete edastamiseks seadme sisend- ja väljundviigudest.

MÖÖDA

Bypass on ühebitine register, mida kasutatakse andmete edastamiseks TDI-st – TDO. Seega võimaldab see vooluringis täiendavaid seadmeid testida minimaalse üldkuluga.

ID KOODID

Seda tüüpi andmeregister sisaldab nii ID-koodi kui ka seadme versiooninumbrit. Seega võimaldavad need andmed ühendada seadme selle BSDL-failiga (Boundary Scan Description Language). See fail sisaldas seadme piiride skannimise konfiguratsiooni üksikasju.

JTAG-i töö seisneb algselt selles, et valitakse käsurežiim, kus üks selle režiimi olekutest „tee” võimaldab operaatoril TDI käsus kella ajada. Pärast seda areneb olekumasin kuni ümberkorraldamiseni. Enamiku juhiste järgmine samm on andmerežiimi valimine. Nii et selles režiimis laaditakse andmed TDO-st lugemiseks TDI kaudu. TDI ja TDO puhul korraldatakse andmeteed vastavalt sisselülitatud juhistele. Kui lugemise/kirjutamise toiming on tehtud, areneb olekumasin uuesti lähtestusolekusse.

Erinevus JTAG ja UART vahel

JTAG-i ja UART-i erinevus hõlmab järgmist.

| JTAG |

UART |

| Mõiste 'JTAG' tähistab ühistestimise tegevusgruppi. | Mõiste ' UART ” tähistab universaalset asünkroonset vastuvõtjat/saatjat. |

| See on sünkroonne liides, mis kasutab välklambi programmeerimiseks sisseehitatud riistvara . | UART on asünkroonne liides, mis kasutab alglaadurit, mis töötab mälus. |

| See on testportide komplekt, mida kasutatakse silumiseks, kuid mida saab kasutada ka püsivara programmeerimiseks (mida tavaliselt tehakse).

|

UART on teatud tüüpi kiip, mis juhib sidet seadmesse, näiteks mikrokontrollerisse, ROM-i, RAM-i jne. Enamasti on see jadaühendus, mis võimaldab meil seadmega suhelda. |

| Need on saadaval nelja tüüpi TDI, TDO, TCK, TMS ja TRST. | Need on saadaval kahte tüüpi loll UART ja FIFO UART. |

| Joint Test Action Group on jadaprogrammeerimine või andmetele juurdepääsu protokoll, mida kasutatakse mikrokontrollerite ja nendega seotud seadmete liidestamiseks. | UART on teatud tüüpi kiip, muidu mikrokontrolleri alamkomponent, mida kasutatakse riistvara pakkumiseks asünkroonse jadavoo genereerimiseks, nagu RS-232/RS-485. |

| JTAG-i komponendid on protsessorid, FPGA-d, CPLD-d , jne. | UART komponendid on CLK generaator, I/O nihkeregistrid, edastus- või vastuvõtupuhvrid, süsteemi andmesiini puhver, lugemise või kirjutamise juhtimisloogika jne. |

JTAG protokolli analüsaator

JTAG-i protokollianalüsaator, nagu PGY-JTAG-EX-PD, on ühte tüüpi protokollianalüsaator, mis sisaldab mõningaid funktsioone hosti ja testitava disaini vahelise suhtluse hõivamiseks ja silumiseks. Seda tüüpi analüsaator on juhtiv instrument, mis võimaldab testimis- ja projekteerimisinseneridel testida JTAG-i konkreetseid konstruktsioone selle spetsifikatsioonide järgi, korraldades PGY-JTAG-EX-PD, nagu Master või Slave, et genereerida JTAG-liiklust ja dekodeerida JTAG-i pakette. Ühise katsetegevuse rühma protokoll.

Funktsioonid

JTAG-protokolli analüsaatori funktsioonid hõlmavad järgmist.

- See toetab kuni 25MH JTAG-i sagedusi.

- See genereerib samaaegselt siini jaoks JTAG-i liikluse ja protokolli dekodeerimise.

- Sellel on JTAG Master võimekus.

- Muutuv JTAG-i andmekiirus ja töötsükkel.

- Kasutaja määratud TDI ja TCK viivitused.

- Hostarvuti USB 2.0 või 3.0 liides.

- Protokolli dekodeerimise tõrkeanalüüs

- Protokolli dekodeeritud siini ajastusskeem.

- Pidev protokolliandmete voogesitus hostarvutisse suure puhvri pakkumiseks.

- Protokolli tegevuste loend.

- Erinevatel kiirustel saab mitme andmekaadri genereerimise kombineerimiseks kirjutada harjutusskripti.

Ajastusskeem

The JTAGi ajastusskeem protokoll on näidatud allpool. Järgmisel diagrammil jääb TDO-tihvt suure impedantsi tingimustesse, välja arvatud nihe-IR/shift-DR kontrolleri oleku ajal.

Shift-IR & Shift-DR kontrolleri tingimustes värskendatakse TDO viiku TCK kahaneval serval Targeti kaudu ja proovi võetakse TCK kasvaval serval hosti kaudu.

Nii TDI kui ka TMS tihvtidest võetakse lihtsalt proovid TCK kasvaval serval Targeti kaudu. Värskendatakse kahanevas servas, muidu TCK hosti kaudu.

Rakendused

The JTAG rakendused sisaldama järgmist.

- Ühist testimistegevusrühma kasutatakse protsessorites sageli nende emuleerimis- või silumisfunktsioonidesse sisenemise õiguse pakkumiseks.

- Kõik CPLD-d ja FPGA-d kasutavad seda liidesena, et anda juurdepääs oma programmeerimisfunktsioonidele.

- Seda kasutatakse PCB-de testimiseks ilma füüsilise juurdepääsuta

- Seda kasutatakse plaaditaseme tootmistestide jaoks.

Seega on see kõik umbes ülevaade JTAGist – pin konfiguratsioon, rakendustega töötamine. Tööstusstandardit JTAG kasutatakse nii disaini kontrollimiseks kui ka PCB testimiseks pärast tootmist. Siin on teile küsimus, mida JTAG tähistab?