Igapäevases elus puutume kokku erinevat tüüpi elektrooniliste vidinatega. Üks tehnoloogiaid, mis tõi revolutsiooni elektroonika tootmises, on “ Integreeritud vooluring “. See tehnoloogia vähendas elektroonikatoodete suurust, suurendades nende tihedust loogika väravad ühe kiibi kohta. Täna on meil erinevaid IC-de tüüpe ja konfiguratsioone. Ümbruskonnas jälgides leiame, et mõnda IC-d saab kasutada ainult ühe konkreetse rakenduse jaoks, samas kui mõnda IC-d saab ümber programmeerida ja kasutada mitmesuguste rakenduste jaoks. Seda tüüpi IC-d nimetatakse ASIC-deks. Kuid kuidas need erinevad? Kuidas on võimalik neid ümber programmeerida? Miks ei saa mõnda IC-d ümber programmeerida? Hüppa, et leida neile küsimustele vastused.

Mis on ASIC (rakendusspetsiifiline integraallülitus)?

ASICi täielik vorm on Rakenduspõhine integreeritud vooluring. Need vooluringid on rakendusspetsiifilised, st. kohandatud valmistatud IC-d konkreetse rakenduse jaoks. Need on tavaliselt välja töötatud juurtasemest lähtuvalt konkreetse rakenduse nõudest. Mõned põhilised rakenduspõhised integraallülituse näited on kiibid, mida kasutatakse mänguasjades, kiip, mida kasutatakse mälu ja mikroprotsessori ühendamiseks jne. Neid kiipe saab kasutada ainult selle rakenduse jaoks, milleks need on mõeldud. Eeldatavasti need tüüpi IC-d eelistatakse ainult nende toodete puhul, millel on suur tootmisprotsess. Kuna ASIC-id on loodud juurtasemelt, on neil kõrge hind ja neid soovitatakse kasutada ainult suure mahuga toodangu jaoks.

ASIC-i peamine eelis on kiibi suuruse vähenemine, kuna ühe kiibi peale ehitatakse suur hulk ahela funktsionaalseid üksusi. Kaasaegne ASIC sisaldab tavaliselt 32-bitist mikroprotsessor , mäluplokid, võrgulülitused jne ... Sellist tüüpi ASIC-sid tuntakse kui Süsteem kiibil . Tootmistehnoloogia arenguga ja disainimeetodite uurimise suurenemisega töötatakse välja erineva tasemega ASIC-id.

ASIC-i tüübid

ASIC-id liigitatakse vastavalt sellele, kui palju programmeerijal on lubatud kiibil teha.

ASIC-de tüübid

Täielik kohandatud

Seda tüüpi kujunduses on kõik loogikarakud kohandatud konkreetseks rakenduseks. disainer peab skeemide jaoks spetsiaalselt loogilised lahtrid tegema. Kõik ühendamise maskikihid on kohandatud. Nii et programmeerija ei saa kiibi ühendusi muuta ja programmeerimise ajal peab ta teadma vooluahela paigutust.

Üks parimaid kohandatud ASIC-i parimaid näiteid on mikroprotsessor. Seda tüüpi kohandamine võimaldab disaineritel ehitada ühele IC-le mitmesuguseid analoogahelasid, optimeeritud mälurakke või mehaanilisi struktuure. Selle ASIC-i tootmine ja kujundamine on kulukas ning väga aeganõudev. Nende IC-de väljatöötamine võtab aega umbes kaheksa nädalat.

Need on tavaliselt mõeldud kõrgetasemelistele rakendustele. Maksimaalne jõudlus, minimaalne ala ja suurim paindlikkus on Full Custom Design'i peamised omadused. Lõpuks on risk kõrge disainiga, kuna loogikakomponente, takistit jms. Kasutatavaid vooluahela elemente ei testita.

Poolkohandatud

Seda tüüpi kujunduses on loogika lahtrid võetud tavalistest raamatukogudest, st. need ei ole käsitööna valmistatud nagu täielikult kohandatud kujunduses. Mõned maskid on kohandatud, samas kui mõned on võetud eelnevalt kujundatud teegist. Põhinedes teegist võetud loogikarakkude tüübil ja vastastikuste ühenduste jaoks lubatud kohandamise hulgal, jagunevad need ASIC-d kahte tüüpi - standardne lahtripõhine ASIC ja Gate Array-põhine ASIC.

1). Tavaline rakupõhine ASIC

Nende IC teadmiseks andke meile kõigepealt mõista, mida tähistab tavaline rakukogu. Mõned loogikarakud nagu JA väravad, VÕI väravad , multiplekserid, plätud on disainerid eelnevalt kujundanud, kasutades erinevaid konfiguratsioone, standardiseeritud ja salvestatud raamatukogu kujul. See kogu on tuntud kui tavaline rakukogu.

Tavaline rakupõhine ASIC

Tavalistes lahtripõhistes kasutatakse nendest standardsetest teekidest pärinevaid ASIC-i loogikarakke. ASIC kiibil koosnevad standardsed lahtrid või paindlik plokk ridade kujul paigutatud standardsetest lahtritest. Koos nende painduvate plokkidega kasutatakse kiibil megarakke nagu mikrokontrollereid või isegi mikroprotsessoreid. Neid megarakke tuntakse ka megafunktsioonide, süsteemitaseme makrode, fikseeritud plokkide, funktsionaalsete standardplokkidena.

Ülal olev joonis kujutab standardset lahtrit ASIC, millel on üks standardne lahtripind ja neli fikseeritud plokki. Maskikihid on kohandatud. Siin saab disainer paigutada standardsed lahtrid kuhugi. Need on tuntud ka kui C-BIC.

2). Väravamassiivi põhine ASIC

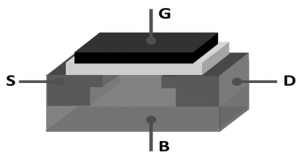

Seda tüüpi poolkohandatud ASIC on eelnevalt määratletud transistorid räni vahvlil. disainer ei saa muuta stantsil olevate transistoride paigutust. Baasimassiiv on väravamassiivi ettemääratud muster ja baasrakk on baasimassiivi väikseim korduv lahter.

Projekteerijal on kohustus muuta ainult transistoride omavahelist ühendust, kasutades stantside esimest paari metallkihti. Disainer valib värava massiivi raamatukogu seast. Neid nimetatakse sageli maskeeritud väravate massiiviks. Gate Array põhised ASIC-d on kolme tüüpi. Need on kanaliseeritud värava massiiv, kanal vähem väravate massiiv ja struktureeritud väravate massiiv.

a). Kanalivärava massiiv

Seda tüüpi väravate massiivi korral jääb transistoriridade vahele juhtmestikuruum. Need on sarnased CBIC-ile, kuna plokkide ühendamiseks on jäetud ruumi, kuid kanaliseeritud väravasüsteemi lahtriread on fikseeritud kõrgusega, samas kui CBIC-is saab seda ruumi reguleerida.

Kanaliga väravate massiiv

Selle värava massiivi mõned põhijooned on - see väravate massiiv kasutab ühendamiseks ridade vahel ettemääratud tühikuid. Tootmisaeg on kaks päeva kuni kaks nädalat.

b). Kanal vähem väravate massiivi

Lahtriridade vahel marsruutimiseks pole vaba ruumi, nagu nähtub kanaliseeritud väravasüsteemist. Siin toimub marsruutimine väravamassiivi lahtrite ülevalt, kuna saame kohandada metalli 1 ja transistoride vahelist ühendust. Marsruutimiseks jätame transistorid marsruudil olles kasutamata. Tootmisaeg on umbes kaks nädalat.

Kanal vähem väravate massiivi

c). Struktureeritud väravate massiiv

Seda tüüpi väravamassiivil on sisseehitatud plokk koos väravamassiivi ridadega, nagu ülal näha. Struktureeritud väravate massiivi CBIC on suurema pindalatõhususega. Nagu Masked gate array, on ka need madalama hinnaga ja kiirema pöördega. Siin piirab manustatud funktsiooni fikseeritud suurus struktureeritud värava massiivi piirangut. Näiteks, kas see väravamassiiv sisaldab ala, mis on reserveeritud 32-bitise kontrolleri jaoks, kuid kui rakenduses vajame ainult ala 16-bitise kontrolleri jaoks, läheb ülejäänud ala raisku. Kõigi väravate massiivi tööaeg on kaks päeva kuni kaks nädalat ja kõigil on kohandatud vastastikune ühendus.

Struktureeritud väravate massiiv

Programmeeritav ASIC

Programmeeritavaid ASIC-sid on kahte tüüpi. Need on PLD ja FPGA

PLD-d (programmeeritavad loogikaseadmed)

Need on standardsed rakud, mis on kergesti kättesaadavad. Saame programmeerida PLD-d rakenduse osa kohandamiseks, nii et neid peetakse ASIC-iks. PLD programmeerimiseks saame kasutada erinevaid meetodeid ja tarkvara. Need sisaldavad tavalist loogikarakkude maatriksit, tavaliselt programmeeritavat massiiviloogikat koos klappide või riividega. Siin on ühendused olemas ühe suure plokina.

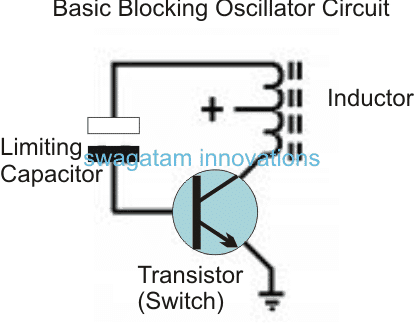

PROM on selle IC tavaline näide. EPROM kasutab omavahel ühendamiseks MOS-transistore, nii et kõrgepinge abil saame selle programmeerida. PLD-del pole kohandatud loogikarakke ega need ole omavahel ühendatud. Neil on kiire disainipöörde.

Programmeeritavad loogikaseadmed

FPGA-d (väli programmeeritav väravate massiiv)

Kus PLD-del on loogikarakkudena programmeeritav massiivi loogika FPGA on värava massiivi sarnane paigutus. PLD-d on väiksemad ja vähem keerukad kui FPGA-d. Tänu oma paindlikkusele ja omadustele asendab FPGA TTL mikroelektroonilistes süsteemides. Disainilahendus on vaid paar tundi.

Välja programmeeritav väravate massiiv

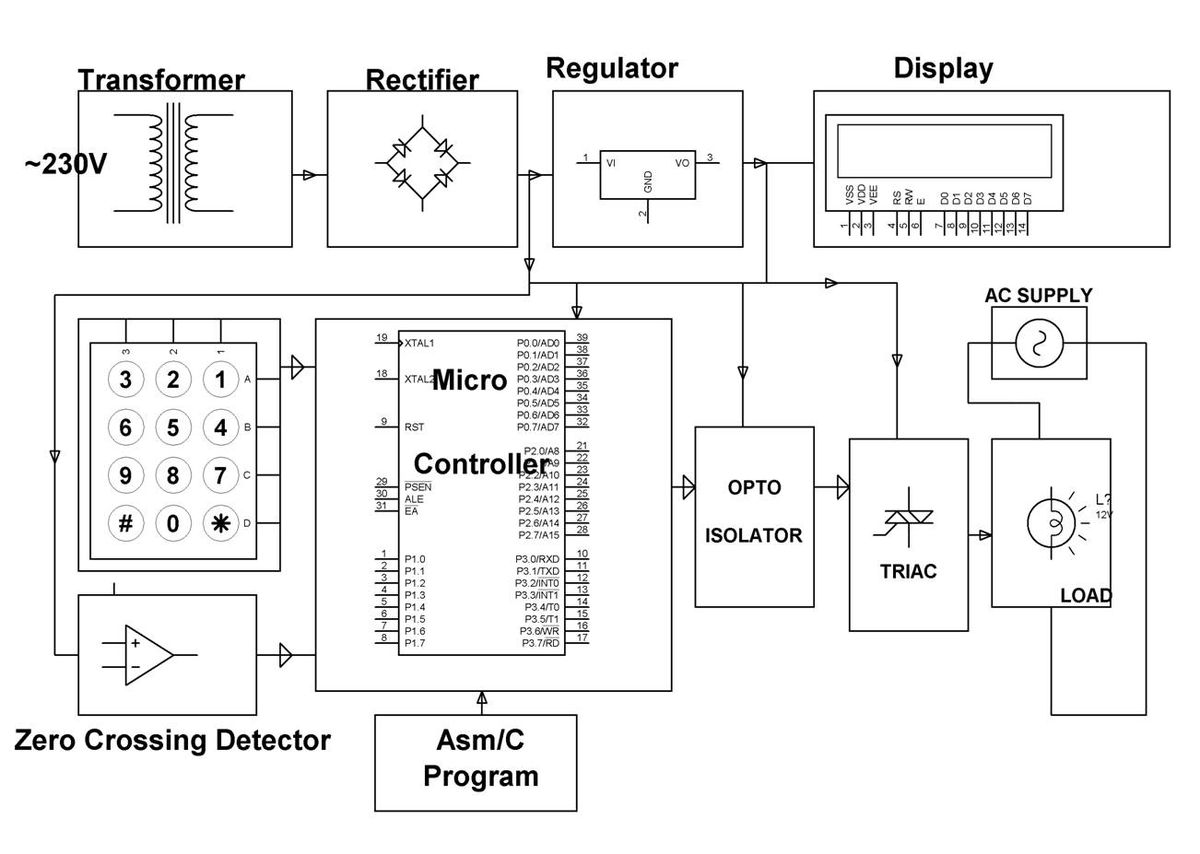

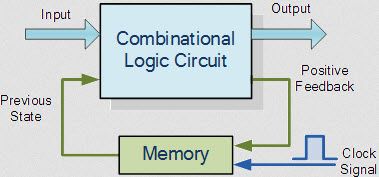

Tuum koosneb programmeeritavatest põhiloogika lahtritest, mis suudavad täita mõlemat kombineeriv ja järjestikune loogika . Mõne meetodi abil saame loogikarakke programmeerida ja omavahel ühenduda. Põhiloogika lahtrid on ümbritsetud programmeeritavate ühenduste maatriksiga ja südamikku ümbritsevad programmeeritavad sisend- / väljundrakud.

FPGA koosneb tavaliselt konfigureeritavatest loogikaplokkidest, konfigureeritavatest I / O-plokkidest, programmeeritavatest ühendustest, kellaahelatest, ALU-st, mälust, dekoodritest.

Oleme näinud erinevat tüüpi ASIC-e saadaval. Mõistame nüüd, kui kõik need kohandused ja ühendused on tootmise käigus tehtud.

Rakendusspetsiifilise integreeritud vooluahela (ASIC) kujundusvoog

ASIC-i kavandamine toimub järk-järgult. Seda sammude järjekorda nimetatakse ASICi disain Voolu. Disainivoo etapid on toodud allpool vooskeemil.

ASICi disainivoog

Kujundus: Selles etapis rakendatakse disaini mikroarhitektuuri riistvarakirjelduse keelte abil, näiteks VHDL, Verilog ja System Verilog.

Loogika süntees: Selles etapis koostatakse HDL-i abil kasutatavate loogikarakkude, vastastikuste ühenduste tüüpide ja kõigi muude rakenduse jaoks vajalike osade võrk.

Süsteemi jaotamine: Selles etapis jagame suuresti suurusega stantsid ASIC-suurusteks tükkideks.

Paigutuseelne simulatsioon: Selles etapis tehakse simulatsioonitesti, et kontrollida, kas disain sisaldab vigu.

Korruse planeerimine: Selles etapis on kiibil paigutatud netlist'i plokid.

Paigutus: Selles etapis otsustatakse lahtrite asukoht plokis.

Marsruutimine: Selles etapis ühendatakse plokid ja lahtrid. Ekstraheerimine: Selles etapis määrame kindlaks ühendamise elektrilised omadused nagu takistuse väärtus ja mahtuvuse väärtus.

Paigutusejärgne simulatsioon: Enne mudeli esitamist tootmise jaoks tehakse see simulatsioon, et kontrollida, kas süsteem töötab koos ühenduste koormusega korralikult.

ASIC-i näited

Olles teadnud ASIC-i erinevaid omadusi, vaatame nüüd mõningaid ASIC-i näiteid.

Tavaline lahtripõhine ASIC: LCB 300k, 500k ettevõttelt LSI Logic Company, SIG1, 2, 3 perekonda ettevõttelt ABB Hafo Inc., GCS90K ettevõttest GCS Plessey.

Gate Array tooted: AUA20K ettevõttelt Harris Semiconductor, SCX6Bxx ettevõttelt National Semiconductors, TGC / TEC perekonnad ettevõttelt Texas Instruments.

PLD tooted: PAL perekond Advanced Micro Devices, GAL perekond firmalt Philips Semiconductors, XC7300 ja EPLD firmalt XILINX.

FPGA tooted: XC2000, XC3000, XC4000, XC5000 seeria firmalt XILINX, pASIC1 QuickLogicust, MAX5000 Alterast.

ASIC-i rakendused

ASICi ainulaadsus on elektroonika tootmise murranguliseks muutnud. Need vähendasid matriitside suurust, suurendades samal ajal loogika väravad ühe kiibi kohta. ASIC-sid eelistatakse tavaliselt kõrgetasemeliste rakenduste jaoks. ASIC kiipi kasutatakse satelliitide IP-südamikena, ROM-i tootmiseks, Mikrokontroller ning mitmesuguseid rakendusi meditsiini- ja teadussektoris. ASICi üks populaarsemaid rakendusi on BITCOIN MINER.

Bitcoin Miner

Krüptoraha kaevandamine nõuab suuremat võimsust ja kiiret riistvara. Üldotstarbeline protsessor ei suuda suurel kiirusel pakkuda nii suurt arvutusvõimsust. ASICi bitcoini kaevurid on spetsiaalselt loodud emaplaatidesse sisse ehitatud kiibid ja toiteallikad , mis on ehitatud ühtseks üksuseks. See on sihipäraselt loodud riistvara kuni bitcoini kaevandamise kiipide tasemeni. Need üksused saavad käivitada ainult ühe krüptoraha algoritmi. Eeldatavalt erinevat tüüpi krüptoraha jaoks vajame teist kaevurit.

ASIC-i eelised ja puudused

The ASIC-i eelised sisaldama järgmist.

- ASICi väike suurus muudab selle keerukate suuremate süsteemide jaoks suureks valikuks.

- Kuna suur arv ahelaid on ehitatud üle ühe kiibi, põhjustab see kiireid rakendusi.

- ASIC-l on madal energiatarve.

- Kuna need on kiibil olev süsteem, on ahelad kõrvuti. Nii et erinevate vooluringide ühendamiseks on vaja väga minimaalset marsruutimist.

- ASIC-il pole ajastusprobleeme ja tootmisjärgset konfiguratsiooni.

The ASIC puudused sisaldama järgmist.

- Kuna need on kohandatud kiibid, pakuvad need programmeerimisel vähe paindlikkust.

- Kuna need kiibid tuleb kujundada juurtasemelt, on nende ühiku hind kõrge.

- ASIC-l on suurem aeg turuväärtuseni.

ASIC vs FPGA

ASIC-i ja FPGA vahe sisaldab järgmist.

ASIC | FPGA |

| Pole ümber programmeeritav | Ümber programmeeritav |

| Eelistatud suure mahuga lavastuste jaoks | Eelistatud väikese mahuga lavastuste jaoks |

| Need on rakenduspõhised | Kasutatakse süsteemi prototüüpidena |

| Energiatõhus nõuab vähem energiat | Vähem energiatõhusaks kasutamiseks on vaja rohkem energiat |

| Need on püsilülitused, mida ei saa aeg-ajalt täiendada. | Väga sobilik rakenduste jaoks, kus vooluahelat tuleb aeg-ajalt täiendada, näiteks mobiiltelefoni kiibid, tugijaamad jne |

Seega on see kõik ülevaade Rakenduspõhine integreeritud vooluring . ASIC-i leiutamine on tohutult muutnud elektroonika kasutamist. Kasutame ASIC-i oma igapäevaelus mitmesuguste rakenduste näol. Milliste ASIC-i rakendustega olete kokku puutunud? Mis tüüpi ASIC-iga olete töötanud?