The väljatransistor (FET) on elektrooniline seade, milles elektriväli kasutatakse voolu voolu reguleerimiseks. Selle rakendamiseks rakendatakse seadme värava ja allika klemmide vahel potentsiaalset erinevust, mis muudab äravoolu ja allika klemmide vahelist juhtivust, põhjustades kontrollitud voolu voolamist üle nende klemmide.

FET-sid kutsutakse unipolaarsed transistorid kuna need on mõeldud töötama ühe kandja tüüpi seadmetena. Saadaval on erinevat tüüpi välitransistore.

Sümbol

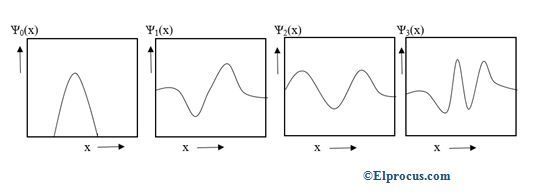

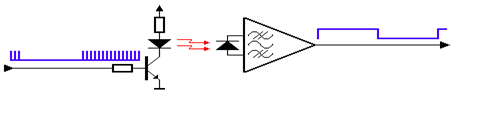

N-kanaliga ja p-kanaliga JFET-ide graafilisi sümboleid saab visualiseerida järgmistel joonistel.

Võite selgelt märgata, et n-kanaliga seadme sissepoole suunatud noolemärgid tähistavad suunda, milles maG(väravavool) peaks voolama siis, kui p-n ristmik oli ettepoole kallutatud.

P-kanaliga seadme puhul on tingimused identsed, välja arvatud noolemärgi suuna erinevus.

FET ja BJT erinevus

Väljatransistor (FET) on kolme klemmiga seade, mis on mõeldud mitmesuguste ahelarakenduste jaoks, mis täiendavad suurel määral BJT-transistori omadusi.

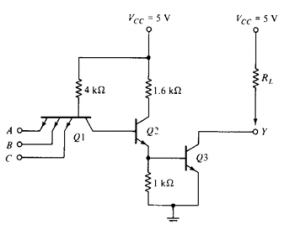

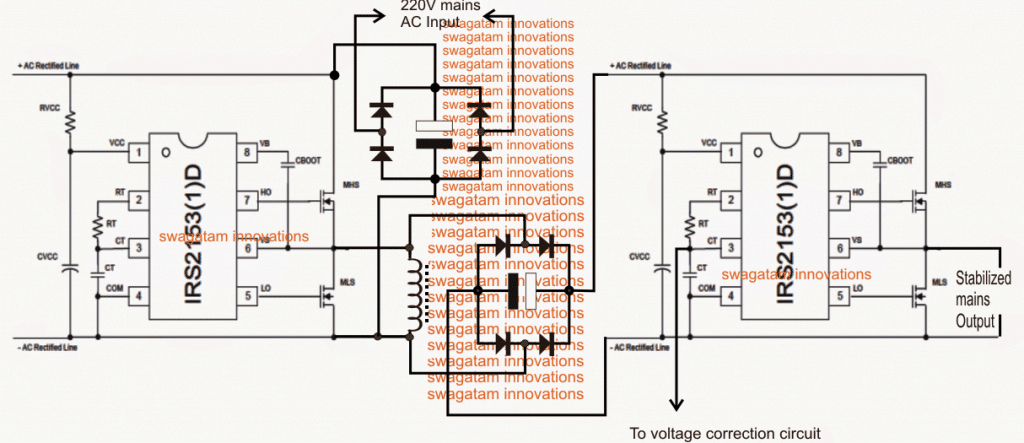

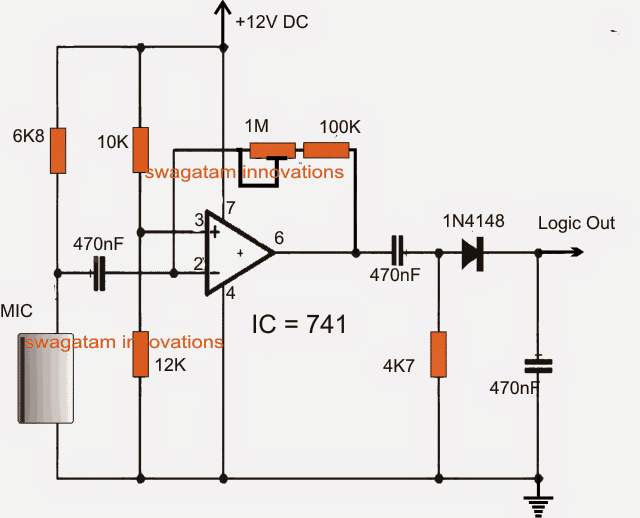

Ehkki leiate olulisi erinevusi BJT-de ja JFET-ide vahel, on tegelikult mitu sobivat omadust, millest räägitakse järgmistes aruteludes. Peamine erinevus nende seadmete vahel on see, et BJT on vooluga juhitav seade, nagu on kujutatud joonisel 5.1a, samal ajal kui JFET transistor on pinge abil juhitav seade, nagu on näidatud joonisel 5.1b.

Lihtsustatult öeldes praegune ICjoonisel 5.1a on I taseme vahetu funktsioonB. FET-i jaoks on vool I sõltuv pingest VGSsisendahelale, nagu on näidatud joonisel 5.1b.

Mõlemal juhul reguleerib väljundahela voolu sisendahela parameeter. Ühes olukorras praegune tase ja teises rakendatud pinge.

Nii nagu bpolaarsete transistoride npn ja pnp, leiate ka n-kanalilised ja p-kanalilised väljatransistorid. Kuid peaksite meeles pidama, et BJT transistor on bipolaarne seade, mille eesliide on bi-, mis näitab, et juhtivuse tase sõltub kahest laengukandjast, elektronist ja aukudest.

FET seevastu on a unipolaarne seade mis sõltub ainult kas elektroni (n-kanaliga) või ava (p-kanaliga) juhtivusest.

Fraasi „väljaefekt” võib seletada järgmiselt: kõik me oleme teadlikud püsimagneti jõust, mis meelitab metallfileid magneti poole ilma igasuguse füüsilise kontaktita. Üsna sarnasel viisil tekitavad FET-is elektrivälja olemasolevad laengud, mis mõjutavad väljundkontuuri juhtivust ilma otsese kontakti kontrollitavate ja kontrollitavate suuruste vahel. Tõenäoliselt on FET-i üks kõige olulisemaid omadusi selle kõrge sisendtakistus.

Vahemikus 1 kuni mitusada megahmi ületab see oluliselt BJT konfiguratsioonide normaalseid sisendtakistuse vahemikke, mis on lineaarse vahelduvvõimendi mudelite väljatöötamisel äärmiselt oluline omadus.

Kuid BJT-l on suurem tundlikkus sisendsignaali variatsioonide suhtes. See tähendab, et väljundvoolu muutus on BJT-de puhul oluliselt suurem kui FET-de puhul nende sisendpinge sama muutuse korral.

Seetõttu võib BJT võimendite tavaline vahelduvvoolu pingetõus olla FET-idega võrreldes palju suurem.

Üldiselt on FET-id tunduvalt soojuskindlamad kui BJT-d ja on ka BJT-dega võrreldes sageli väiksema struktuuriga, mis muudavad need spetsiaalselt integreeritud vooluahelatena manustamiseks (IC)kiibid.

Mõne FET-i struktuuriomadused seevastu võimaldavad neil olla füüsiliste kontaktide suhtes eriti tundlikud kui BJT-d.

Veel BJT / JFET-i suhteid

- BJT V jaoksBE= 0,7 V on oluline tegur selle konfiguratsiooni analüüsi alustamiseks.

- Samamoodi parameeter IG= 0 A on JFET-ahela analüüsimisel tavaliselt esimene asi.

- BJT konfiguratsiooni jaoks olenBon sageli esimene tegur, mis osutub vajalikuks kindlaks teha.

- Samamoodi on JFET-i puhul tavaliselt VGS.

Selles artiklis keskendume JFET-idele või ristmiku väljatransistoridele, järgmises artiklis käsitleme metallioksiidi-pooljuhi välja-efekti transistorit või MOS-FET-i.

JFETIDE EHITUS JA OMADUSED

Nagu me Earlieti õppisime, on JFET-il 3 juhtmega. Üks neist kontrollib voolu kahe teise vahel.

Nii nagu BJT-d, kasutatakse ka JFET -ides n-kanaliga seadet silmatorkavamalt kui p-kanalilisi analooge, kuna n seadet kipuvad p-seadmega võrreldes olema tõhusamad ja kasutajasõbralikumad.

Järgmisel joonisel näeme n-kanaliga JFET-i põhistruktuuri või konstruktsiooni. Näeme, et n-tüüpi kompositsioon moodustab p-tüüpi kihtide põhikanali.

N-tüüpi kanali ülemine osa ühendatakse ohmkontakti kaudu terminali abil, mille nimi on äravool (D), samal ajal kui sama kanali alumine sektsioon on ühendatud ka ohmkontakti kaudu teise terminaliga, mille nimi on allikas (S).

Paar p-tüüpi materjali on ühendatud värava (G) tähisega terminaliga. Põhimõtteliselt leiame, et äravoolu- ja allikaklemmid on ühendatud n-tüüpi kanali otstega. Väravaklemm on ühendatud p-kanalilise materjali paariga.

Kui jfetile pole rakendatud pinget, on selle kaks p-n ristmikku ilma igasuguste kõrvalekalleteta. Selles olukorras on igal ristmikul ammendumispiirkond, nagu on näidatud ülaltoodud joonisel, mis näeb välja nagu dioodi p-n piirkond, ilma et see oleks kallutatud.

Vee analoogia

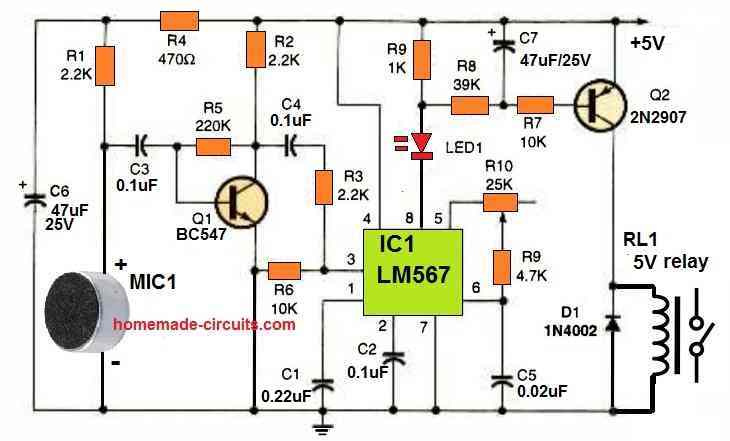

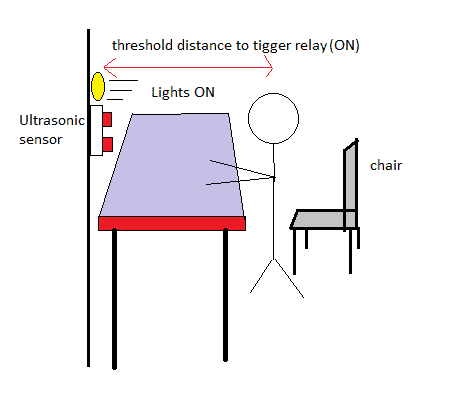

JFET-i töö- ja juhtimisoperatsioone saab mõista järgmise veeanaloogia abil.

Siin saab veesurvet võrrelda äravoolust allika suunas rakendatud pinge suurusega.

Vee voolu saab võrrelda elektronide vooluga. Kraani suu jäljendab JFET-i lähteklemmi, samas kui kraani ülemine osa, kuhu vesi sisse surutakse, kujutab JFET-i äravoolu.

Kraaninupp toimib nagu JFET-i värav. Sisendpotentsiaali abil kontrollib see elektronide voolu (laengut) äravoolust allikani, nii nagu kraaninupp juhib vee voolu suuavas.

JFET-i struktuurist näeme, et äravoolu ja lähteklemmid asuvad n-kanali vastaskülgedel ja kuna termin põhineb elektronide voolul, võime kirjutada:

VGS= 0 V, VDSMõni positiivne väärtus

Joonisel 5.4 näeme positiivset pinget VDSrakendatakse üle n-kanali. Tingimuse V loomiseks ühendatakse väravaterminal otse allikagaGS= 0V. See võimaldab väraval ja lähteklemmidel olla ühesuguse potentsiaaliga ning tulemuseks on iga p-materjali alumise otsa ammendumispiirkond täpselt nii, nagu näeme ülaltoodud esimeses skeemis ilma erapoolikuseta.

Niipea kui pinge VDD(= VDS), tõmmatakse elektronid äravooluklemmi suunas, tekitades voolu ID tavapärase voolu, nagu on näidatud joonisel 5.4.

Laengu voolu suund näitab, et äravoolu ja allika vool on suurusjärgus (ID= MinaS). Vastavalt joonisel 5.4 kujutatud tingimustele näib laengu voog üsna piiramatu ja seda mõjutab ainult äravoolu ja allika vaheline n-kanali takistus.

Võite täheldada, et ammendumispiirkond on mõlema p-tüüpi materjali ülemise osa ümber suurem. See piirkonna suuruse erinevus on ideaalis seletatav joonisel 5.5. Kujutame ette, et n-kanalil on ühtlane takistus, selle võiks jagada joonisel 5.5 näidatud sektsioonideni.

Praegune IDvõib ehitada kanali kaudu pingepiirkonnad, nagu on näidatud samal joonisel. Selle tulemusel hakatakse p-tüüpi materjali ülemist piirkonda tagurpidi kallutama umbes 1,5 V taseme võrra, kusjuures alumine piirkond on ainult vastupidise kallutusega 0,5 V võrra.

Punkt, et p-n ristmik on kogu kanali ulatuses vastupidise kallutusega, tekitab null ampriga väravavoolu, nagu on näidatud samal joonisel. See omadus, mis viib minuniG= 0 A on JFETi oluline tunnus.

Nagu VDSpotentsiaali suurendatakse 0-lt mõne voltini, vool suureneb vastavalt Ohmi seadusele ja I jooniseleDrida 5DSvõib välja näha nagu tõestatud joonisel 5.6.

Joonestamise võrdlev sirgus näitab, et V madala väärtusega piirkondade puhulDS, on takistus põhimõtteliselt ühtlane. Nagu VDStõuseb ja läheneb tasemele, mida nimetatakse VP-ks joonisel 5.6, laienevad ammendumispiirkonnad, nagu on näidatud joonisel 5.4.

Selle tulemuseks on kanali laiuse näiline vähenemine. Vähenenud juhtivus viib vastupanu suurenemiseni, mis põhjustab joonisel 5.6 toodud kõvera.

Mida horisontaalsemaks kõver muutub, seda suurem on takistus, mis näitab, et takistus muutub horisontaalses piirkonnas 'lõpmatute' oomide suunas. Kui VDSsuureneb määral, kus näib, et kaks ammendumispiirkonda võivad 'kokku puutuda', nagu on näidatud joonisel 5.7, tekitab olukorra, mida nimetatakse näpistamiseks.

Summa, mille võrra VDSarendab seda olukorda nimetatakse näpistama pinge ja seda sümboliseerib VPnagu on näidatud joonisel 5.6. Üldiselt on sõna näputäis eksitav, kuna see viitab praegusele I-leDon 'kinni pigistatud' ja langeb 0 A. Nagu on tõestatud joonisel 5.6, ei tundu see antud juhul vaevalt ilmne. MinaDsäilitab küllastustaseme, mida iseloomustatakse kui IDSSjoonisel 5.6.

Tõde on see, et kanalit on jätkuvalt väga vähe, vool on märkimisväärselt kõrge.

Punkt, kuhu ID ei kuku näpistama ja säilitab joonisel 5.6 näidatud küllastustaseme, kinnitatakse järgmise tõestusega:

Kuna äravooluvool puudub, välistab n-kanaliga materjali potentsiaalsete tasemete mitmekesisuse määramine vastupidise eelarvamuse muutuva hulga määramiseks p-n ristmikul. Lõpptulemuseks oli vallandunud ammendumispiirkonna jaotuse kaotus näpistama alustuseks.

Kui suurendame V-dDSüle VP, piki kanalit pikeneb tiheda kontakti piirkond, kus kaks ammendumispiirkonda üksteisega kokku puutuvad. Kuid ID tase on endiselt sisuliselt muutumatu.

Seega hetk VDSon suurem kui Vlk, omandab JFET vooluallika omadused.

Nagu on näidatud joonisel 5.8, määratakse JFET-i vool I juuresD= MinaDSS, kuid pinge VDSkõrgem kui VP tuvastatakse ühendatud koormusega.

IDSS-i tähistuse valimine põhineb asjaolul, et see on Drain to Source vool, millel on lühisühendus värava ja allika vahel.

Edasine uurimine annab meile järgmise hinnangu:

MinaDSSon JFET-i suurim äravooluvool ja see on määratud tingimustega VGS= 0 V ja VDS> | VP |

Pange tähele, et joonisel 5.6 VGSon 0V kõvera kogu venituse korral. Järgmistest osadest õpime, kuidas joonise 5.6 atribuudid muutuvad V taseme mõjutamiselGSon mitmekesine.

VGS <0V

Üle värava ja allika rakendatud volatiiki tähistatakse kui VGS-i, mis vastutab JFET-toimingute kontrollimise eest.

Kui võtame BJT näite, täpselt nagu I kõveradCvs VSEEmääratakse I erineva taseme jaoksB, samamoodi I kõveradDvs VDSerinevate V-tasemete jaoksGSsaab luua JFET-i kolleegi jaoks.

Selleks on väravaterminal seatud jätkuvalt madalamale potentsiaalile allika potentsiaali tasemest madalamale.

Viidates allpool olevale joonisele 5.9, rakendatakse vähendatud V jaoks üle värava / allika klemmide -1 VDStasemel.

Negatiivse potentsiaalse eelarvamuse eesmärk VGSon välja töötada ammendumispiirkonnad, mis sarnanevad V olukorragaGS= 0, kuid oluliselt vähenenud V juuresDS.

See põhjustab väravas küllastuspunkti madalama V-tasemegaDSnagu on näidatud joonisel 5.10 (VGS= -1 V).

Vastav I küllastustaseDvõib leida vähenenud ja tegelikult lihtsalt väheneb V-naGSmuudetakse negatiivsemaks.

Jooniselt 5.10 näete selgelt, kuidas nõrgenemispinge langeb paraboolse kujuga VGSmuutub üha negatiivsemaks.

Lõpuks, kui VGS= -Vlk, muutub see küllalt negatiivseks küllastustaseme määramiseks, mis on lõpuks 0 mA. Sellel tasemel on JFET täielikult „välja lülitatud“.

V taseGSmis põhjustab ID0 mA saavutamiseks iseloomustab VGS= VPkus VPon negatiivne pinge n-kanaliga seadmete jaoks ja positiivne pinge p-kanaliga JFET-de jaoks.

Tavaliselt võidakse kuvada enamik JFET-i teabelehti näpistama pinge määratletud kui VGS (väljas)V asemelP.

Ülaltoodud joonisel näpistatava lookuse parema külje ala on moonutustevaba signaali saavutamiseks lineaarsetes võimendites tavapäraselt kasutatav koht. Seda piirkonda nimetatakse üldiselt konstantse voolu, küllastuse või lineaarse amplifikatsiooni piirkond.

Pingega juhitav takisti

Piirkonda, mis asub samal joonisel näpistatava lookuse vasakul küljel, nimetatakse oomiline piirkond või pingega juhitav takistuspiirkond.

Selles piirkonnas saab seadet tegelikult käitada muutuva takistusena (näiteks automaatse võimenduse juhtimise rakenduses), mille takistust saab juhtida rakendatud värava / allika potentsiaali kaudu.

Näete, et iga kõvera kalle, mis tähistab ka JFET-i äravoolu / allika takistust V-leDS

Kui muudame VGS-i negatiivse potentsiaaliga kõrgemaks, muutub iga kõvera kalle üha horisontaalsemaks, näidates proportsionaalselt vastupanu taset.

Järgmise võrrandi kaudu suudame saada hea algse lähenduse takistuse tasemele VGS-pinge suhtes.

p-kanaliga JFET töötab

P-kanaliga JFET-i sisemine paigutus ja ehitus on täpselt identne n-kanalilise analoogiga, välja arvatud see, et p- ja n-tüüpi materjalide piirkonnad on vastupidised, nagu allpool näidatud:

Voolu suundi võib vaadelda ka ümberpööratuna koos pinge VGS ja VDS tegelike polaarsustega. P-kanaliga JFET-i korral on kanal piiratud vastusena värava / allika positiivse potentsiaali suurenemisele.

Topeltindeksiga tähis V-leDSpõhjustab V jaoks negatiivse pingeDS, nagu on näidatud joonisel 5.12. Siit leiate mindDSSpingel 6 mA, samal ajal kui pinge pingel V juuresGS= + 6V.

Palun ärge hämmingus, kuna teil on V miinusmärkDS. See lihtsalt näitab, et allikal on suurem potentsiaal kui äravoolul.

Näete, et kõrge V kõveradDStase tõuseb järsult väärtusteni, mis näivad piiramatud. Näidatud vertikaalne tõus sümboliseerib lagunemissituatsiooni, mis tähendab, et kanaliseadet läbivat voolu juhib antud ajahetkel täielikult väline vooluring.

Kuigi n-kanaliga seadme puhul pole seda joonisel 5.10 näha, võib see olla piisavalt kõrge pinge korral võimalus.

Selle piirkonna saab kõrvaldada, kui VDS (max)on märgitud seadme andmelehelt ja seade on konfigureeritud nii, et tegelik VDSväärtus on väiksem kui mis tahes V puhul märgitud väärtusGS.

Eelmine: 5 parimat uuritud 40-vatist võimendusahelat Järgmine: 2N3055 andmeleht, Pinout, rakendusahelad