Digitaalse riistvara projekteerimisprotsess on viimastel aastatel intensiivselt muutunud. Nii saab väikseid digitaalahelasid rakendada PAL-ide ja PLA-de abil. Iga seadet kasutatakse erinevate ahelate rakendamiseks mis ei vaja rohkem kui konkreetses kiibis pakutavate i / ps, o / ps ja tootetingimuste arv. Need kiibid on ebapiisavad üsna tagasihoidlike mõõtmetega, toetades tavaliselt vastastikust arvu sisendeid ja väljundeid, mis ei ületa 32. Nende rohkem sisendeid ja väljundeid vajavate vooluahelate kujundamiseks võib kasutada kas arvukaid PLA-sid / PAL-e või muidu stiilseimat tüüpi kiipi saab kasutada nimega CPLD (keeruline programmeeritav loogikaseade). CPLD kiip sisaldab mitu kiibiplokki ühel kiibil koos juhtmestiku sisemiste ressurssidega vooluahelate kinnitamiseks. Iga vooluplokk on võrreldav PLA või PAL-ga.

Mis on keeruline programmeeritav loogikaseade?

CPLD akronüüm on „Komplekssed programmeeritavad loogikaseadmed”, see on üks selline integraallülitus et rakenduste disainerid kavandavad digitaalse riistvara nagu mobiiltelefonid juurutamiseks. Need saavad hakkama teadlikult kõrgemate kujundustega kui SPLD-d (lihtsad programmeeritavad loogikaseadmed), kuid pakuvad vähem loogikat kui FPGA-d ( väljaga programmeeritavad väravate massiivid ). CPLD-d sisaldavad arvukalt loogikaplokke, millest igaüks sisaldab 8-16 makrarakku. Kuna iga loogikaplokk täidab kindlat funktsiooni, on kõik loogikalises plokis olevad makrarakud täielikult ühendatud. Sõltuvalt kasutamisest võivad need plokid olla üksteisega ühendatud või mitte.

Kompleksne programmeeritav loogikaseade

Enamikul CPLD-del (keerukad programmeeritavad loogikaseadmed) on makrarakud, millel on loogikafunktsiooni summa ja valikainete arv FF (flip-flop) . Kombinatiivne loogikafunktsioon toetab olenevalt kiibist 4–16 tootetingimust koos kaasava ventilaatoriga. CPLD-d erinevad ka vahetuste registrite ja loogikaväravate poolest. Seetõttu võib FPGA-de asemel kasutada tohutu hulga loogikaväravatega CPLD-sid. Teine CPLD spetsifikatsioon tähistab tooteterminite arvu, mida makrotsell suudab saavutada. Tootetingimused on konkreetse loogikafunktsiooni täitvate digitaalsignaalide tulemus.

CPLD-d on saadaval mitmes IC-paketi vormis ja loogikaperekonnas. CPLD-d erinevad ka toitepinge, töövoolu, ooterežiimi voolu ja energia hajumise poolest. Lisaks on need saadaval mitmesuguste mäluhulkade ja mitmesuguse mälutoega. Tavaliselt väljendatakse mälu bittides / megabittides. Mälu tugi koosneb ROM-ist, RAM-ist ja kahe pordi RAM-ist. See sisaldab ka CAM-i (sisuga adresseeritav mälu), samuti FIFO-mälu (esimene sisse, esimene välja) ja LIFO mälu (viimane sisse, viimane välja).

Kompleksse programmeeritava loogikaseadme arhitektuur

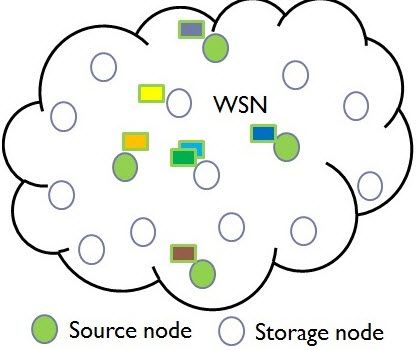

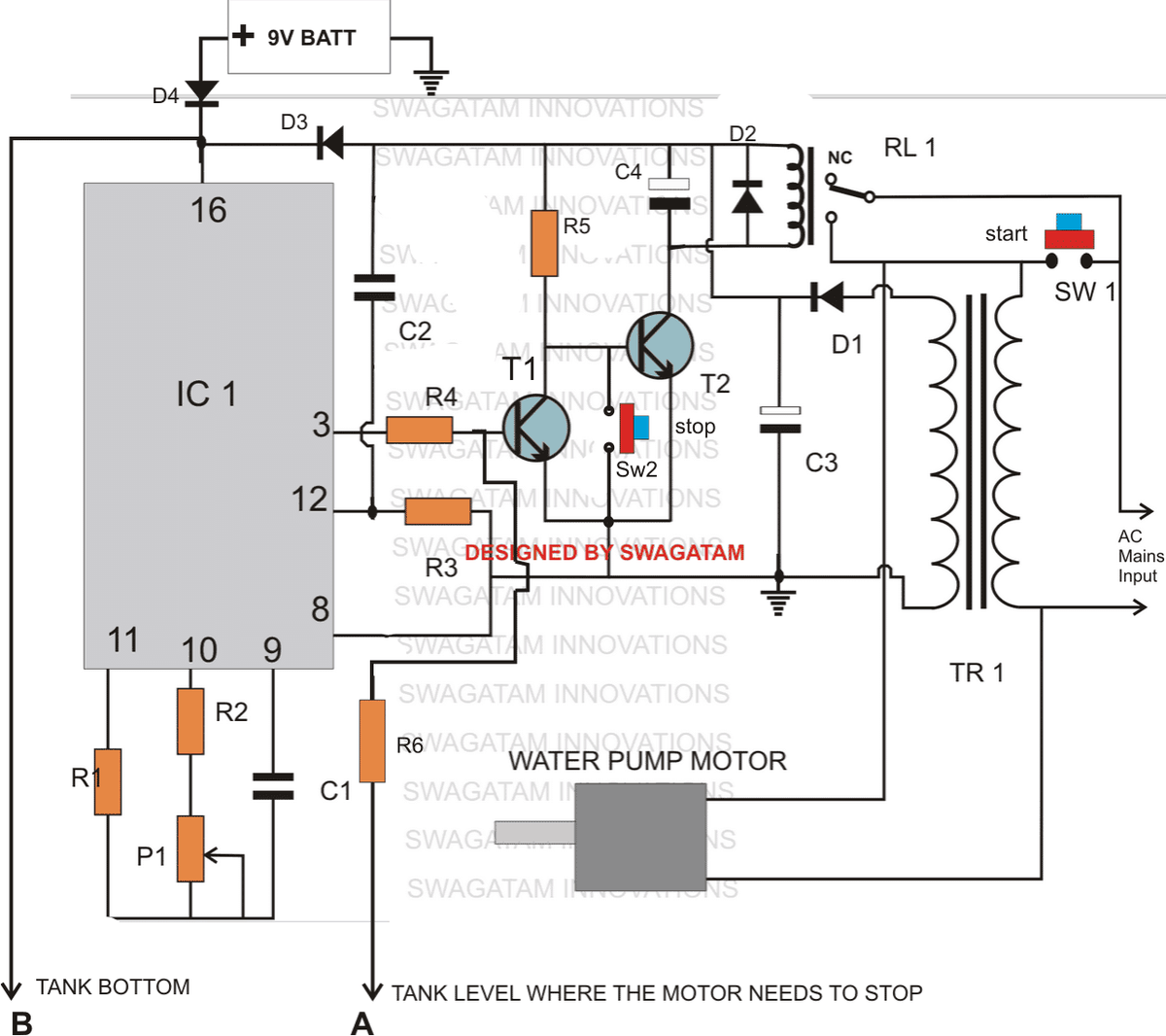

Kompleksne programmeeritav loogikaseade koosneb programmeeritavate FB-de (funktsionaalsete plokkide) rühmast. Nende funktsionaalsete plokkide sisendid ja väljundid on ühendatud GIM-i (globaalse ühendamise maatriks) abil. See ühendamismaatriks on ümberkonfigureeritav, nii et saame funktsionaalsete plokkide vahelisi kontakte muuta. Seal on mõned sisend- ja väljundplokid, mis võimaldavad meil ühendada CPLD välismaailmaga. CPLD arhitektuur on näidatud allpool.

Üldiselt näeb programmeeritav FB välja nagu loogikaväravate massiiv , kus saab programmeerida AND-väravate massiivi ja OR-väravad on stabiilsed. Kuid igal tootjal on funktsionaalse ploki kujundamiseks oma mõtteviis. Loetletud o / p leiate OR-värava väljunditest saadud tagasisidesignaalide abil.

CPLD arhitektuur

CPLD programmeerimisel kodeeritakse kujundus kõigepealt Verilogi või VHDL keeles, kui kood on (simuleeritud ja sünteesitud. Sünteesi käigus valitakse CPLD mudel (sihtseade) ja toodetakse tehnoloogiapõhine kaardistusvõrgu loend. See loend võib olla lähedal - sobitamine ehtsale CPLD arhitektuurile, kasutades koha ja marsruudi protsessi, mis tavaliselt saavutatakse ettevõtte CPLD ettevõtte oma asukoha ja marsruudi tarkvaraga. Seejärel teeb operaator mõned kinnitusprotsessid. Kui kõik on hea, kasutab ta CPLD-d, muul juhul ta korraldab selle ümber.

CPLD arhitektuuriküsimused

Kaaludes keerukat programmeeritavat loogikaseadet disainis kasutamiseks, võib arvesse võtta järgmisi arhitektuuriprobleeme

- Programmeerimistehnoloogia

- Funktsioonide blokeerimise võime

- Sisend / väljundvõime

Mõned CPLD perekonnad erinevatelt jaemüüjatelt hõlmavad järgmist

- Altera MAX 7000 ja MAX 9000 perekonnad

- ATMEL ATF ja ATV perekonnad

- Võre isp LSI perekond

- Võre (Vantis) MACH perekond

- Xilinx XC9500 perekond

CPLD perekonnad

CPLD rakendused

CPLD-de rakendused hõlmavad järgmist

- Komplekssed programmeeritavad loogikaseadmed sobivad ideaalselt suure jõudlusega kriitiliste juhtimisrakenduste jaoks.

- CPLD-d saab digitaalsetes kujundustes kasutada alglaaduri funktsioonide täitmiseks

- CPLD-d kasutatakse väli programmeeritava väravasüsteemi konfiguratsiooniandmete laadimiseks püsimälust.

- Üldiselt kasutatakse neid väikestes disainirakendustes nagu aadresside dekodeerimine

- CPLD-sid kasutatakse sageli paljudes rakendustes, näiteks kulutustundlikes, akutoitega kaasaskantavates seadmetes, kuna need on väikesed ja kasutavad vähe energiat.

Seega on see kõik keerulise programmeeritava loogikaseadme arhitektuuri ja selle rakenduste kohta. Loodame, et olete sellest kontseptsioonist paremini aru saanud. Lisaks sellele võivad kõik selle kontseptsiooniga seotud küsimused või elektri- ja elektroonikaprojektide elluviimiseks , esitage palun oma väärtuslikud ettepanekud, kommenteerides allolevas kommentaaride jaotises. Siin on teile küsimus, mis vahe on CPLD-l ja FPGA-l?

Foto autorid:

- CPLD wikimedia

- CPLD arhitektuur slidesharecdn